José Fortunato Zuloaga Cachay Consuelo Ivonne Del Castillo Casto Gilberto Carrión Barco Fredy William Campos Flores Lucia Isabel Chamán Cabrera

# Electrónica Digital Para Arquitectura de Computadoras

# José Fortunato Zuloaga Cachay Consuelo Ivonne Del Castillo Casto Gilberto Carrión Barco Fredy William Campos Flores Lucia Isabel Chamán Cabrera

# Electrónica digital para arquitectura de computadoras

Título original: Electrónica digital para arquitectura de computadoras

Primera edición: octubre 2020

© 2020, José Fortunato Zuloaga Cachay Consuelo Ivonne Del Castillo Casto Gilberto Carrión Barco Fredy William Campos Flores Lucia Isabel Chamán Cabrera

Publicado por acuerdo con los autores. © 2020, Editorial Grupo Compás Guayaquil-Ecuador

Grupo Compás es una editorial de la Universidad de Oriente desde el 2017, cada uno de sus textos han sido sometido a un proceso de evaluación por pares externos con base en la normativa del editorial. Este texto ha sido sugerido para su indexación en Latindex, Redib, ErihPlus, mediante ISSN 2600-5743 Folio 28701 Folio Único 24972 Centro de Acopio, Ecuador

El copyright estimula la creatividad, defiende la diversidad en el ámbito de las ideas y el conocimiento, promueve la libre expresión y favorece una cultura viva. Quedan rigurosamente prohibidas, bajo las sanciones en las leyes, la producción o almacenamiento total o parcial de la presente publicación, incluyendo el diseño de la portada, así como la transmisión de la misma por cualquiera de sus medios, tanto si es electrónico, como químico, mecánico, óptico, de grabación o bien de fotocopia, sin la autorización de los titulares del copyright.

Editado en Guayaquil - Ecuador

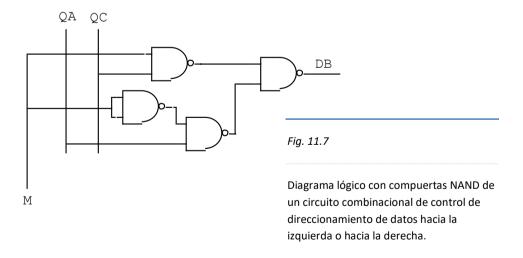

ISBN: 978-9942-33-333-9

Organización de las Naciones Unidas para la Educación, la Ciencia y la Cultura Cátedra UNESCO « Paz, Solidaridad y Diálogo Intercultural », Universitat Abat Oliba CEU

uni Twin

## Índice

| Intro  | ducción    |                                          | 11 |

|--------|------------|------------------------------------------|----|

| Capít  | ulo 1: Fu  | ndamentos de Electrónica Analógica       |    |

| 1.1.   | Magnit     | 13                                       |    |

|        | 1.1.1.     | Carga eléctrica                          |    |

|        | 1.1.2.     | Corriente eléctrica                      | 14 |

|        | 1.1.3.     | Voltaje                                  | 15 |

|        | 1.1.4.     | Ley de Ohm                               | 17 |

|        | 1.1.5.     | Resistencia eléctrica                    | 18 |

|        | 1.1.6.     | Potencia eléctrica                       | 19 |

|        | 1.1.7.     | Energía y potencia                       | 20 |

|        | 1.1.8.     | Corriente alterna                        | 20 |

|        | 1.1.9.     | Generación de corriente alterna          | 21 |

|        | 1.1.10.    | Valores típicos de una señal alterna     | 22 |

|        |            | 1.1.10.1. Frecuencia                     | 22 |

|        |            | 1.1.10.2. Valor eficaz y valor medio     | 23 |

| 1.2.   | Disposi    | 24                                       |    |

|        | 1.2.1.     | Diodos                                   | 25 |

|        | 1.2.2.     | Transistores BJT                         | 28 |

|        |            | 1.2.2.1. Zonas de trabajo del transistor | 29 |

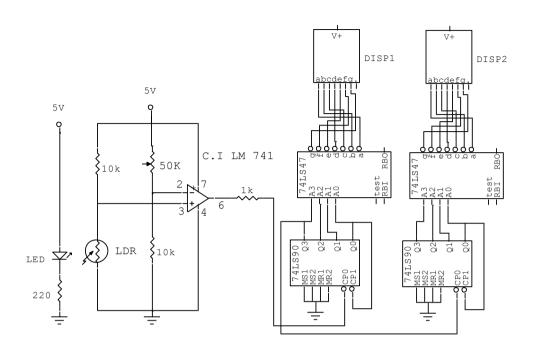

|        | 1.2.3.     | Amplificadores operacionales             | 31 |

| 1.3. 9 | Señales ar | nalógicas y digitales                    | 34 |

|        | 1.3.1.     | Señales analógicas                       | 35 |

|        | 1.3.2.     | Señales digitales                        | 35 |

|        | 1.3.3.     | Lógica digital                           | 35 |

|        | 1.3.4.     | Lógica positiva y lógica negativa        | 36 |

| Prob   | lemas Re   | sueltos № 01                             | 36 |

| Proh   | lemas Pro  | nnuestos Nº 01                           | 45 |

| Capít | tulo 2: Si         | stemas y códigos de numeración                                   |    |

|-------|--------------------|------------------------------------------------------------------|----|

| 2.1.  | Repres             | sentación de datos                                               | 47 |

|       | 2.1.1.             | Representación de números, sistemas de numeración                | 48 |

|       | 2.1.2.             | Sistema de numeración binario                                    | 48 |

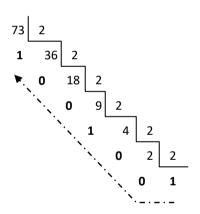

|       | 2.1.3.             | Conversión del sistema binario a decimal y viceversa             | 49 |

|       | 2.1.4.             | Sistema octal y hexadecimal                                      | 51 |

|       | 2.1.5.             | Conversión del sistema octal y hexadecimal a binario y viceversa | 52 |

| 2.2.  | Renres             | sentación de números en formato signo magnitud                   | 54 |

| 2.3.  |                    | os binarios                                                      | 55 |

| 2.5.  | 2.3.1.             |                                                                  | 55 |

|       | 2.3.2.             | _                                                                | 56 |

|       | 2.3.3.             | _                                                                | 57 |

|       | 2.3.4.             |                                                                  | 57 |

|       | 2.3.5.             |                                                                  | 59 |

| 2.4.  |                    | ores de error                                                    | 60 |

|       | 2.4.1.             |                                                                  | 60 |

| Prob  | lemas Re           | esueltos № 02                                                    | 61 |

| Prob  | lemas Pr           | opuestos Nº 02                                                   | 64 |

| Capít | tulo 3: De         | escripción de circuitos digitales                                |    |

| 3.1.  | Tablas             | de verdad                                                        | 65 |

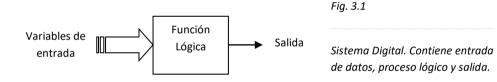

| 3.2.  | Variab             | les y funciones lógicas                                          | 66 |

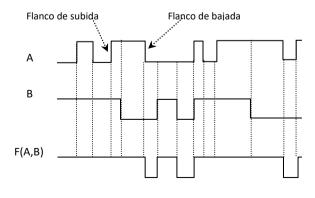

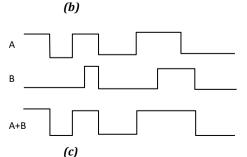

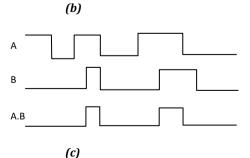

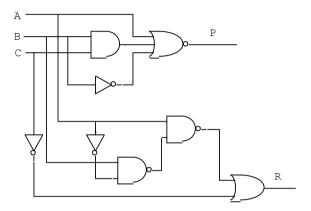

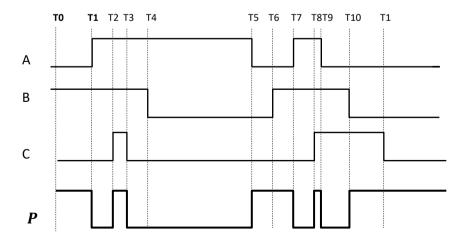

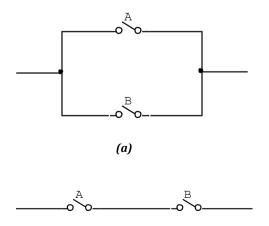

| 3.3.  | _                  | mas de tiempo                                                    | 66 |

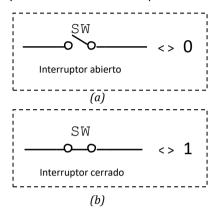

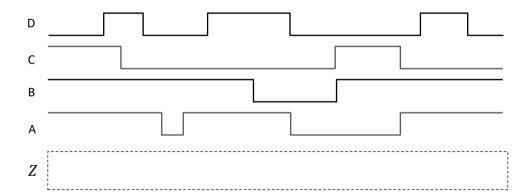

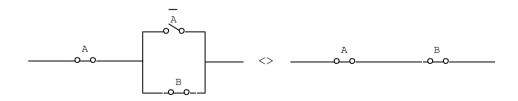

| 3.4.  | Lógica             | de contactos                                                     | 67 |

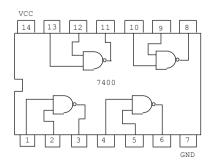

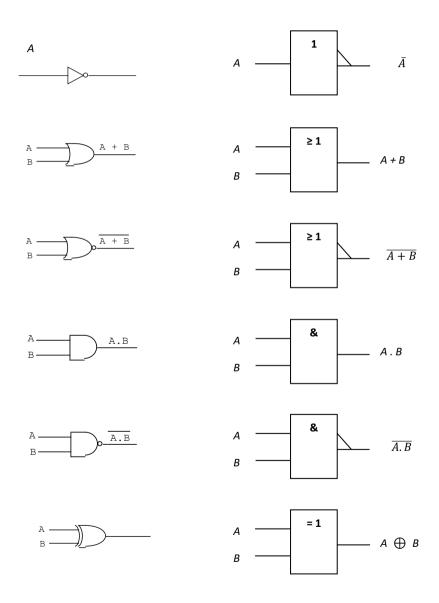

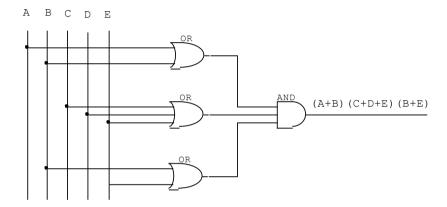

| 3.5.  | Compuertas lógicas |                                                                  |    |

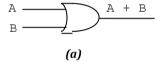

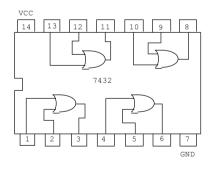

|       | 3.5.1.             | Compuerta lógica OR                                              | 68 |

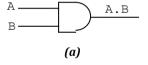

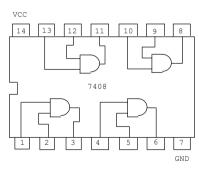

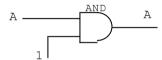

|       | 3.5.2.             | Compuerta lógica AND                                             | 69 |

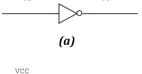

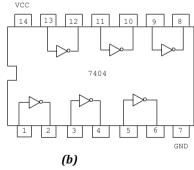

|       | 3.5.3.             | Compuerta lógica NOT                                             | 70 |

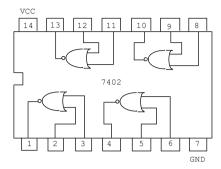

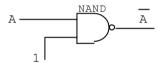

|       | 3.5.4.             | , 9                                                              | 70 |

|       | 3.5.5.             | 1 0                                                              | 71 |

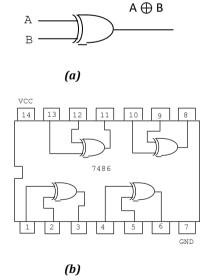

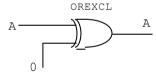

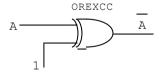

|       | 3.5.6.             | Compuerta lógica OR EXCLUSIVA                                    | 72 |

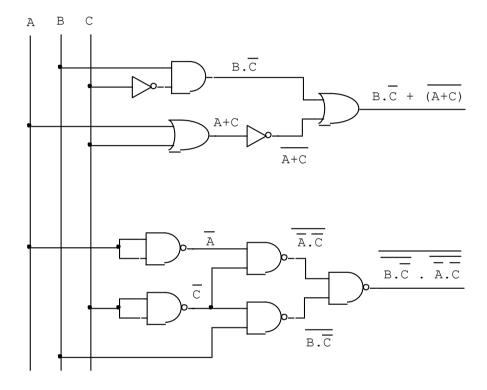

| 3.6.  |                    | sentaciones alternas de compuertas lógicas                       | 73 |

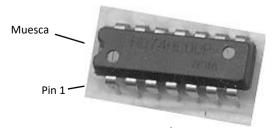

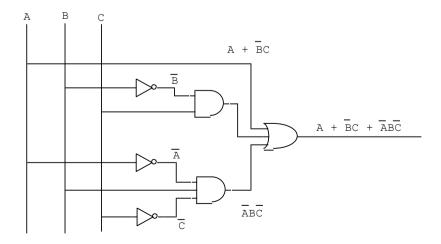

| 3.7.  | -                  | nentación de circuitos                                           | 74 |

| 3.8.  | _                  | mas lógicos                                                      | 74 |

| 3.9.  | _                  | mas esquemáticos                                                 | 75 |

|       |                    | esueltos № 03                                                    | 76 |

| Prob  | lemas Pr           | opuestos № 03                                                    | 81 |

| -     |                    | gebra de Boole                                                   |    |

| 4.1.  | Definio            |                                                                  | 83 |

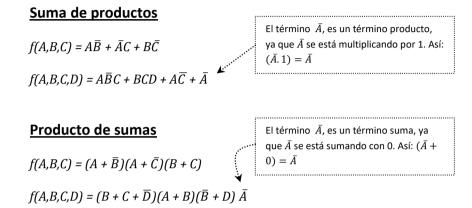

| 4.2.  | -                  | iones de una función lógica                                      | 84 |

| 4.3.  |                    | nas del Álgebra de Boole                                         | 84 |

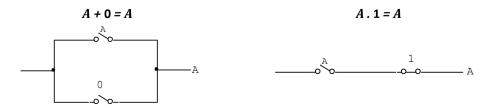

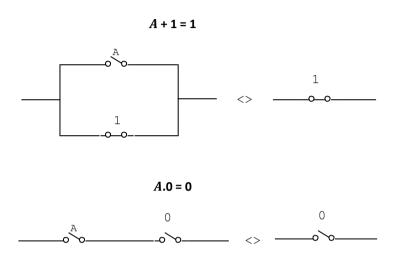

|       | 4.3.1.             | Propiedad de Identidad                                           | 84 |

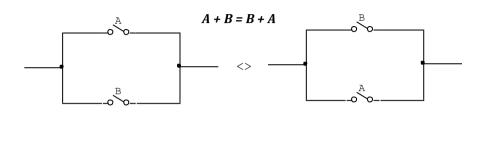

|       | 4.3.2.             | Propiedad conmutativa                                            | 85 |

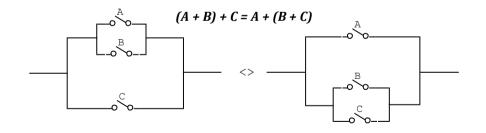

|       | 4.3.3.                                       | Propiedad asociativa                                            | 85  |

|-------|----------------------------------------------|-----------------------------------------------------------------|-----|

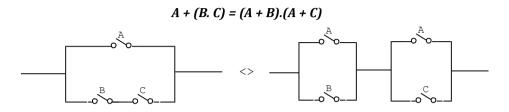

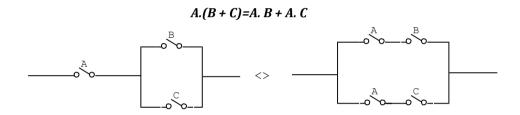

|       | 4.3.4.                                       | Propiedad distributiva                                          | 86  |

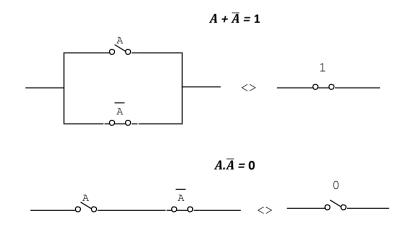

|       | 4.3.5.                                       | Propiedad del complemento                                       | 86  |

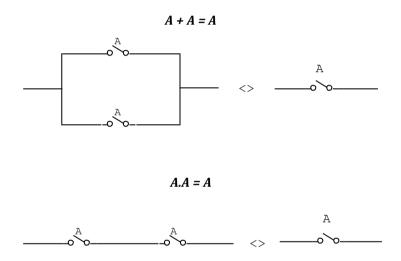

|       | 4.3.6.                                       | Propiedad de idempotencia                                       | 87  |

|       | 4.3.7.                                       | Propiedad de unicidad del complemento                           | 87  |

|       | 4.3.8.                                       | Propiedad de los elementos dominantes                           | 87  |

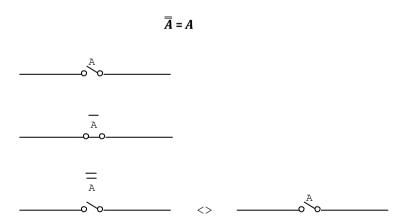

|       | 4.3.9.                                       | Propiedad involutiva                                            | 88  |

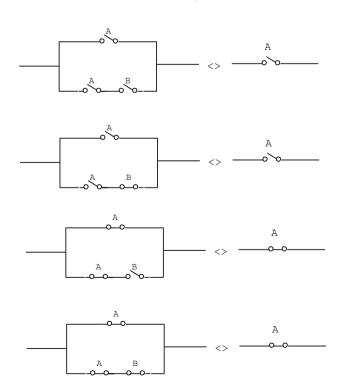

|       | 4.3.10.                                      | Propiedad de absorción                                          | 89  |

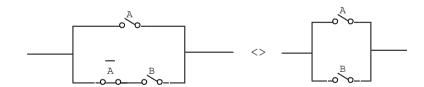

|       | 4.3.11.                                      | Propiedad de consenso                                           | 90  |

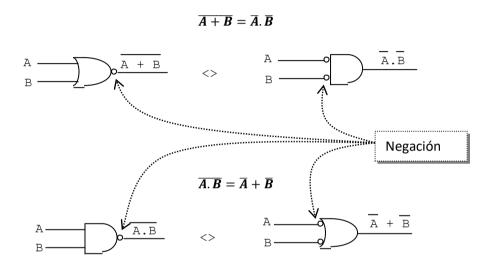

| 4.4.  | Teoremas De Morgan                           |                                                                 |     |

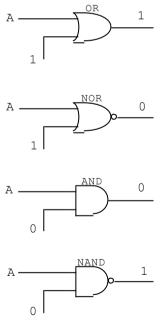

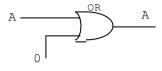

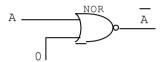

|       | 4.4.1.                                       | Efecto del Teorema de Morgan en las compuertas AND y OR.        | 92  |

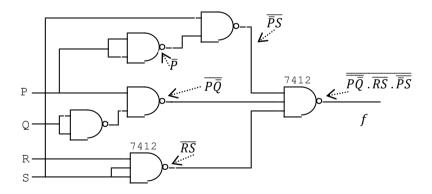

| 4.5.  | Versatil                                     | lidad de las compuertas NAND y NOR                              | 92  |

| 4.6.  | Simplificación de funciones lógicas          |                                                                 |     |

| Prob  | lemas Re                                     | sueltos № 04                                                    | 96  |

| Prob  | lemas Pro                                    | ppuestos № 04                                                   | 103 |

| Capít | ulo 5: Est                                   | andarización y métodos de simplificación de funciones           |     |

| 5.1.  | Formas                                       | canónicas de funciones lógicas                                  | 105 |

|       | 5.1.1.                                       | Expresiones canónicas en suma de productos "minitérminos"       | 107 |

|       | 5.1.2.                                       | Expresiones canónicas en productos de sumas "maxitérminos"      | 109 |

| 5.2.  | Método                                       | o de simplificación de funciones lógicas                        | 111 |

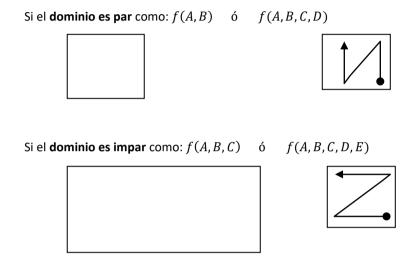

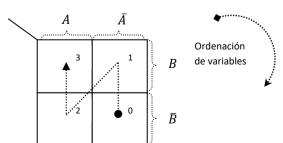

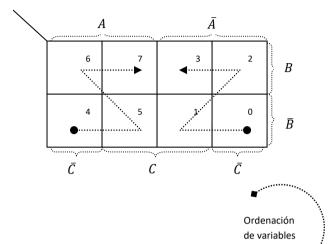

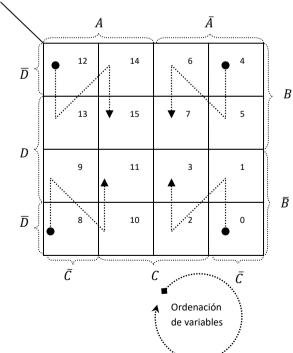

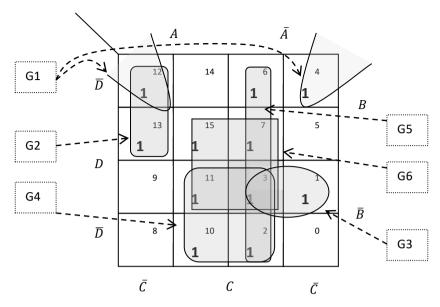

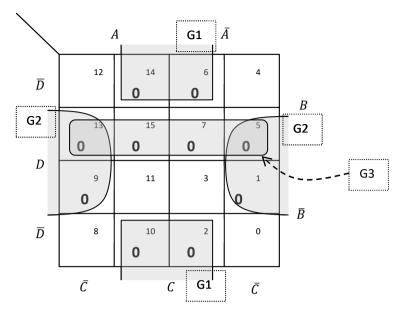

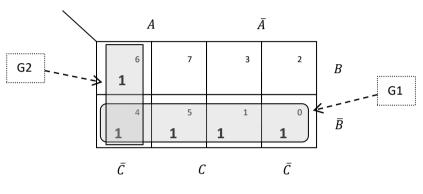

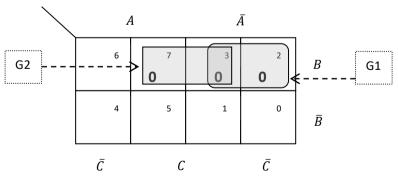

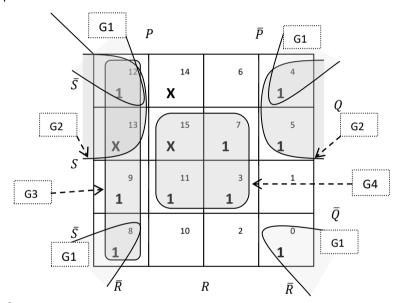

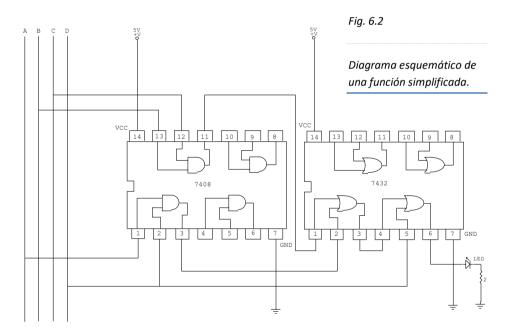

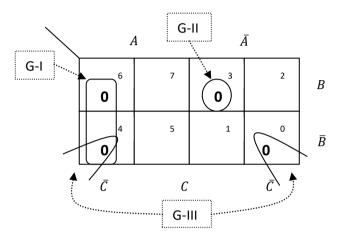

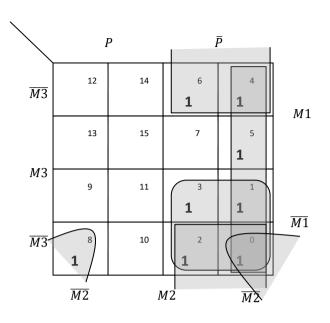

|       | 5.2.1.                                       | Mapas de Karnaugh                                               | 111 |

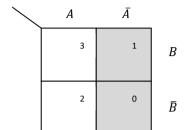

|       |                                              | 5.2.1.1. M.K. de dos variables                                  | 112 |

|       |                                              | 5.2.1.2. M.K. de tres variables                                 | 113 |

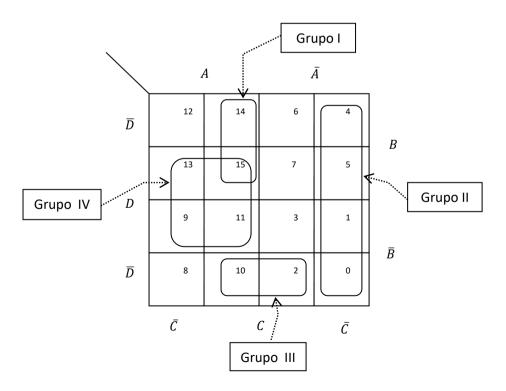

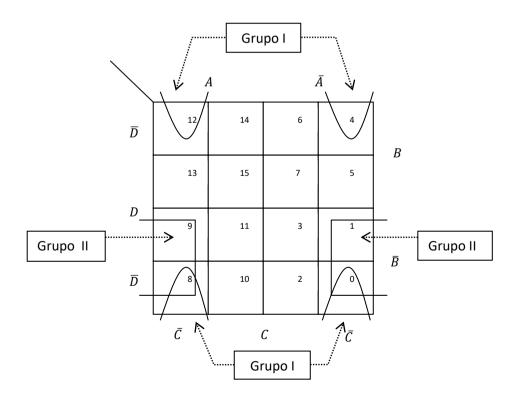

|       |                                              | 5.2.1.3. M.K. de cuatro variables                               | 113 |

| 5.3.  |                                              | cia de las variables en las celdas del M.K.                     | 114 |

| 5.4.  |                                              | de simplificación de funciones lógicas con M.K.                 | 115 |

| 5.5.  |                                              | nes incompletamente especificadas                               | 117 |

|       |                                              | sueltos № 05                                                    | 118 |

| Prob  | lemas Pro                                    | opuestos № 05                                                   | 125 |

| Capít | ulo 6: Cir                                   | cuitos combinacionales y circuitos integrados                   |     |

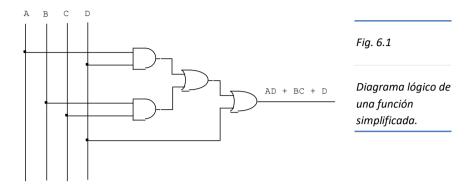

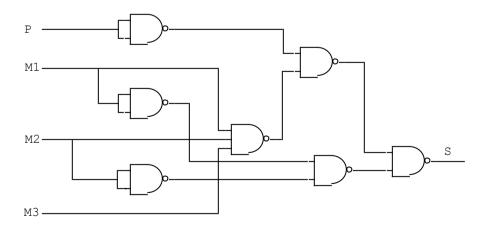

| 6.1.  | Introducción a los circuitos combinacionales |                                                                 | 127 |

| 6.2.  | •                                            | ientación de circuitos combinacionales                          | 127 |

|       | 6.2.1.                                       |                                                                 | 128 |

|       | 6.2.2.                                       | Partiendo de una tabla de verdad                                | 130 |

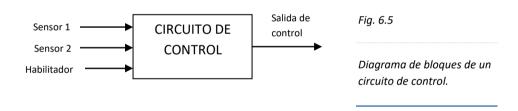

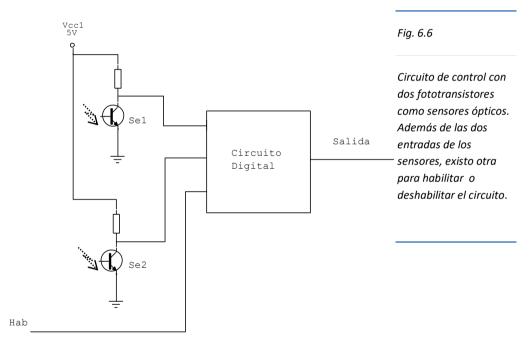

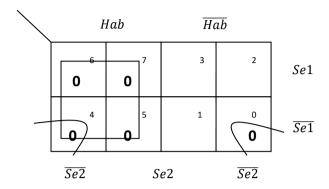

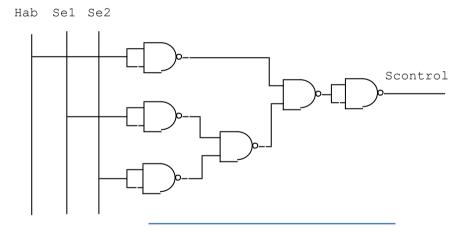

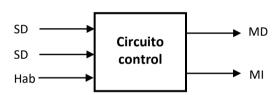

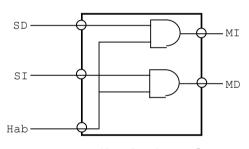

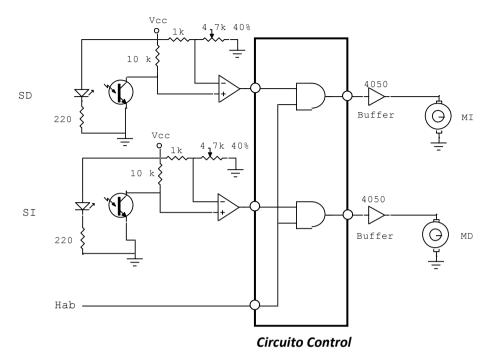

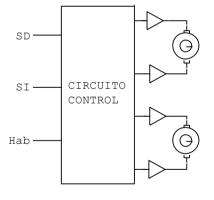

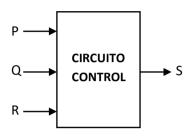

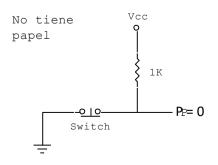

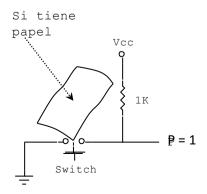

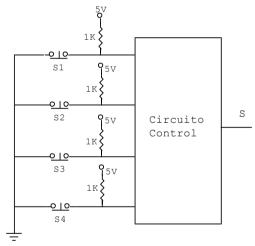

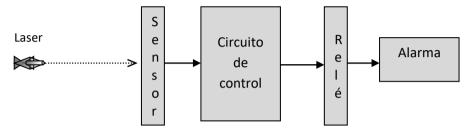

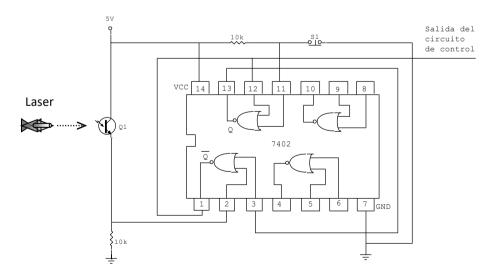

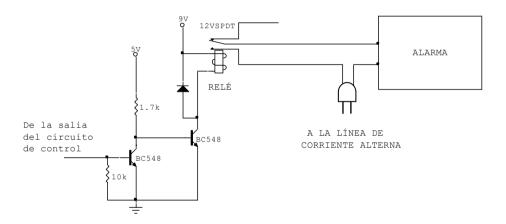

| 6.3.  |                                              | de desarrollo de circuitos de control lógico                    | 133 |

|       | 6.3.1.                                       | Circuitos de habilitación y deshabilitación                     | 133 |

|       | 6.3.2.                                       | Circuitos de control                                            | 134 |

| 6.4.  |                                              | rísticas de los circuitos integrados digitales                  | 138 |

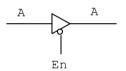

|       | 6.4.1.                                       | Compuertas lógicas con tres estados                             | 138 |

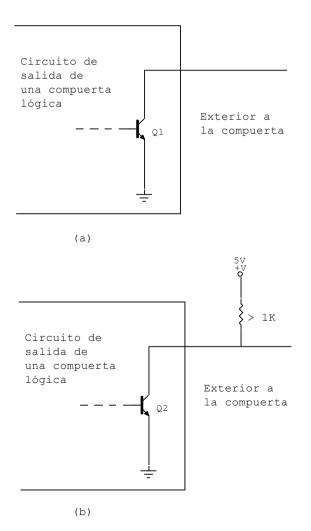

|       | 6.4.2.                                       | Salida de una compuerta en Colector Abierto (Open colector)     | 140 |

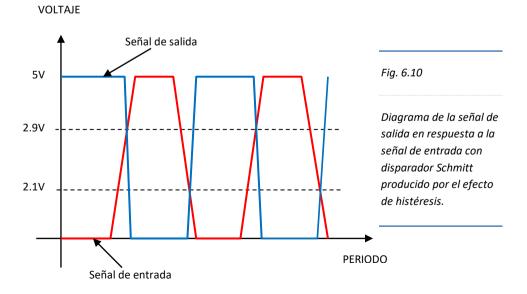

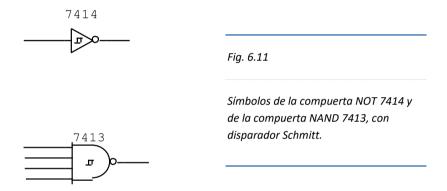

|       | 6.4.3.                                       | Compuertas con entradas de disparador Schmitt (Schmitt trigger) | 141 |

|       |                                              | sueltos Nº 06                                                   | 142 |

| Prob  | lemas Pro                                    | ppuestos № 06                                                   | 154 |

| Capít  | ulo 7: Co                                    | dificadores y multiplexores                                          |     |

|--------|----------------------------------------------|----------------------------------------------------------------------|-----|

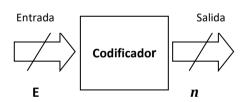

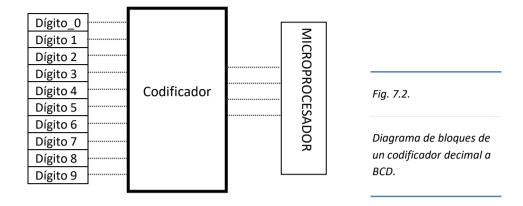

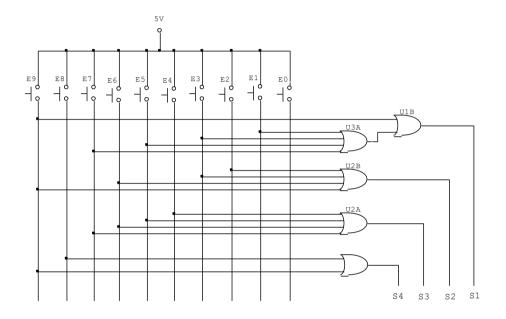

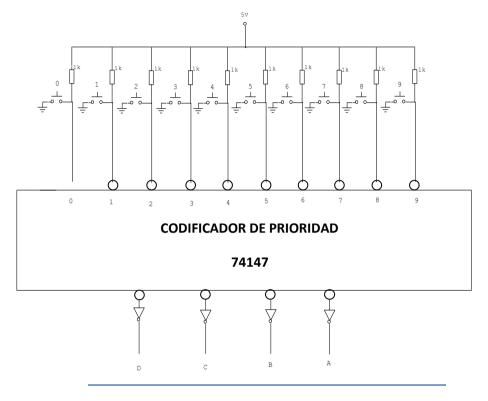

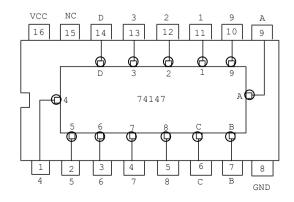

| 7.1.   | Codifica                                     | adores                                                               | 155 |

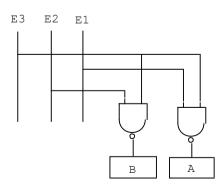

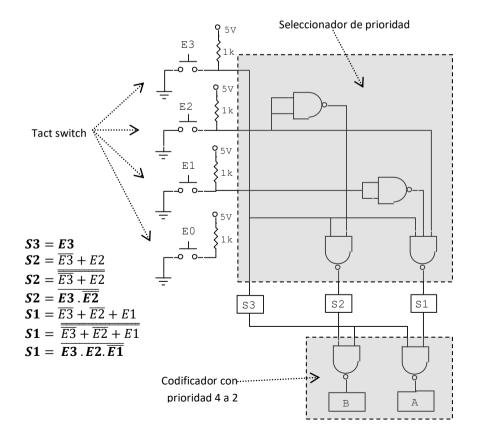

|        | 7.1.1.                                       | Codificadores sin prioridad                                          | 157 |

|        | 7.1.2.                                       | Codificadores con prioridad                                          | 158 |

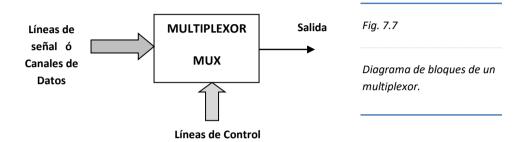

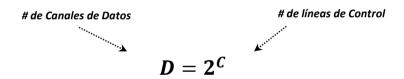

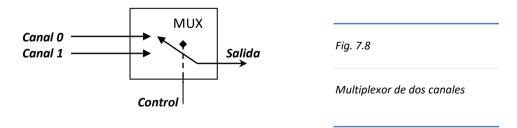

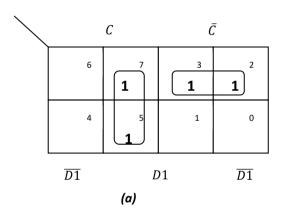

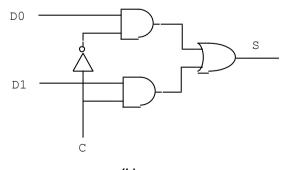

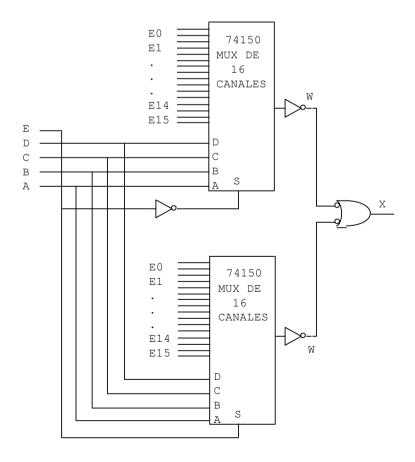

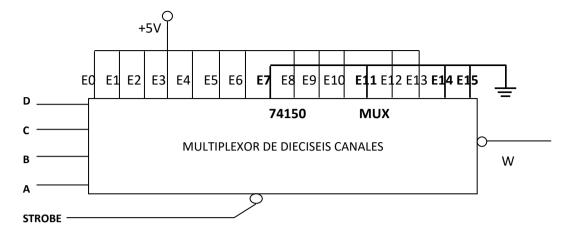

| 7.2.   | Multipl                                      | exores                                                               | 161 |

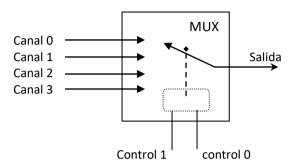

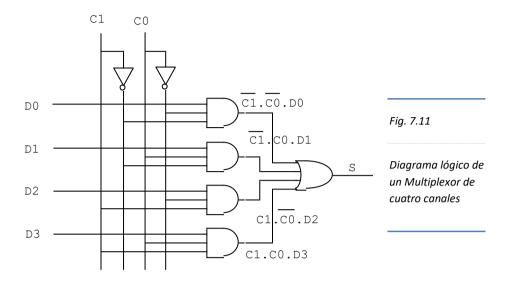

|        | 7.2.1.                                       | Diseño de un multiplexor de cuatro canales                           | 163 |

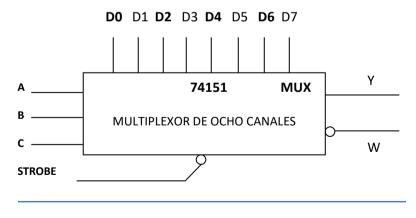

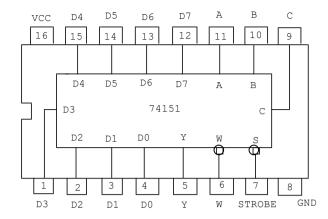

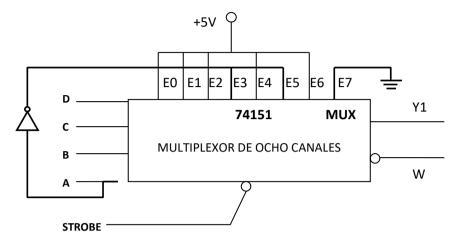

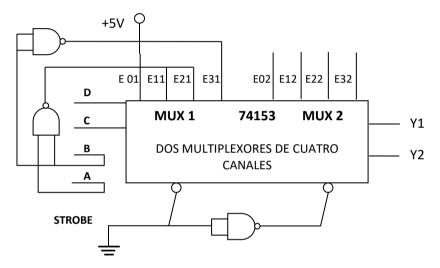

|        | 7.2.2.                                       | Multiplexor comercial de ocho canales                                | 164 |

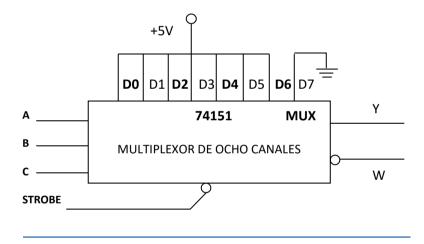

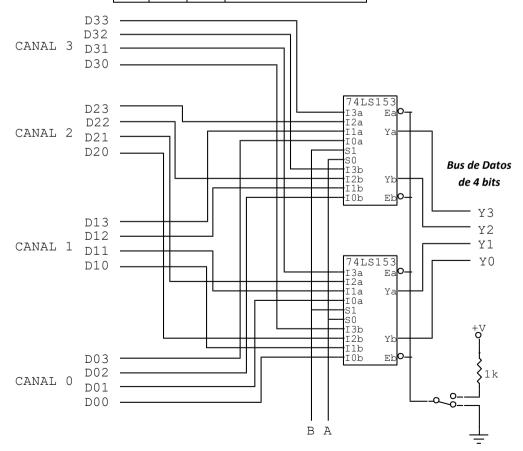

|        | 7.2.3.                                       | Aplicaciones del multiplexor                                         | 165 |

| Proble | emas Re                                      | sueltos № 07                                                         | 167 |

| Probl  | emas Pro                                     | opuestos № 07                                                        | 175 |

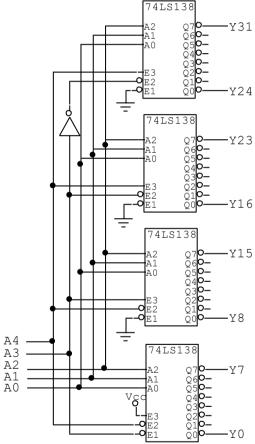

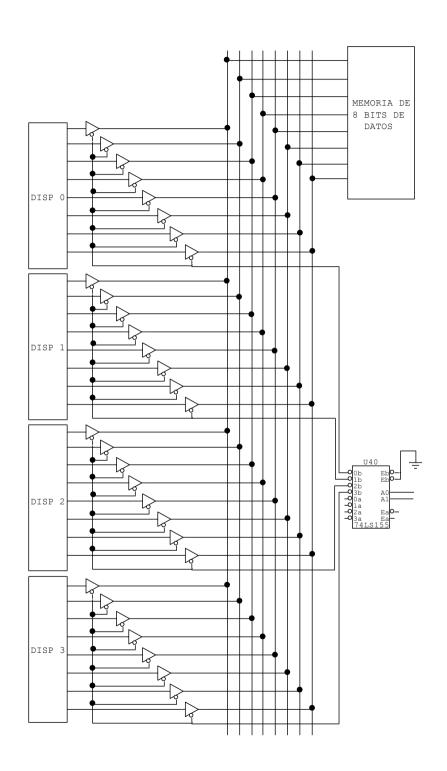

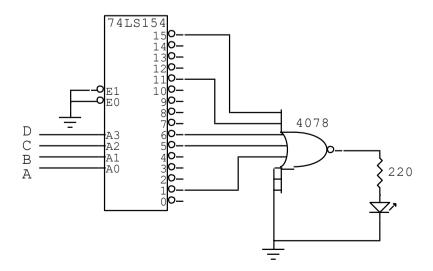

| Capíti | ulo 8: De                                    | codificadores, demultiplexores y comparadores de magnitud            |     |

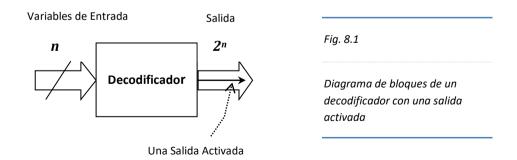

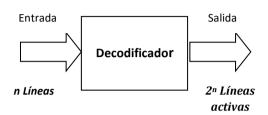

| 8.1.   |                                              | ficadores                                                            | 177 |

| 0.2.   | 8.1.1.                                       |                                                                      | 177 |

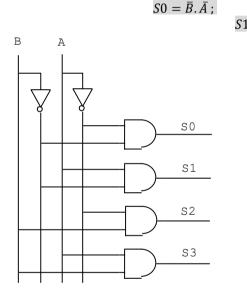

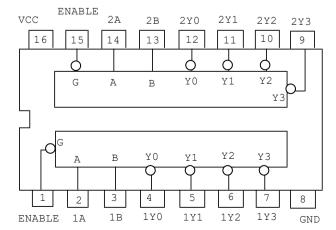

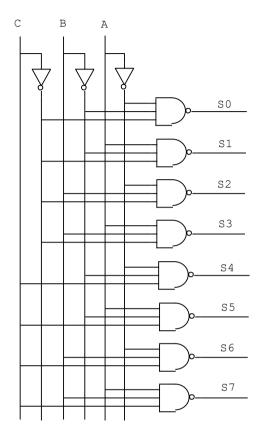

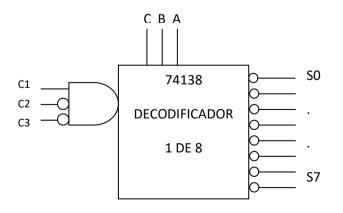

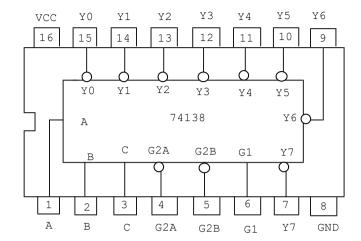

|        |                                              | 8.1.1.1. Diseño de un decodificador de ocho salidas con puertas NAND | 179 |

|        | 8.1.2.                                       | Decodificadores con varias salidas activadas                         | 182 |

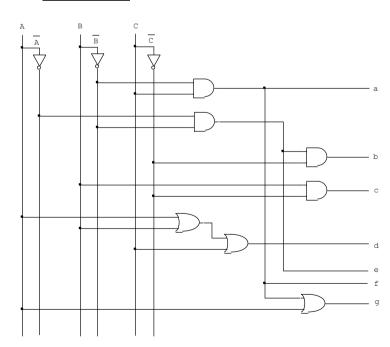

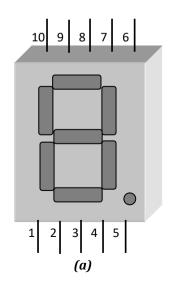

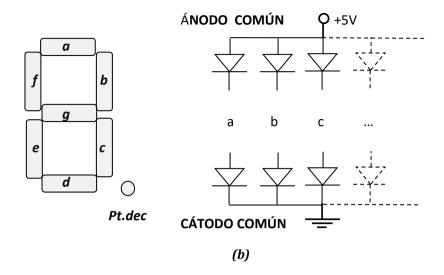

|        |                                              | 8.1.2.1. Visualizador numérico de siete segmentos                    | 182 |

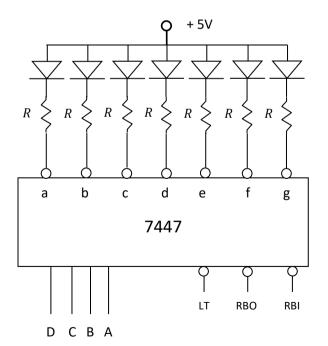

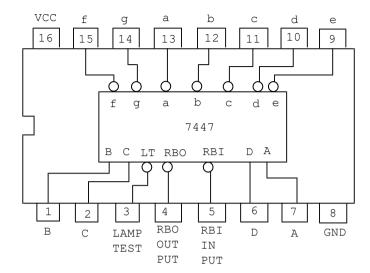

|        |                                              | 8.1.2.2. Decodificadores/controladores de BCD a siete                | 184 |

|        |                                              | segmentos                                                            |     |

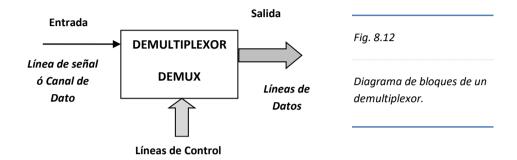

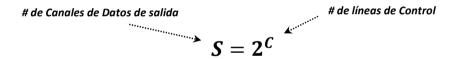

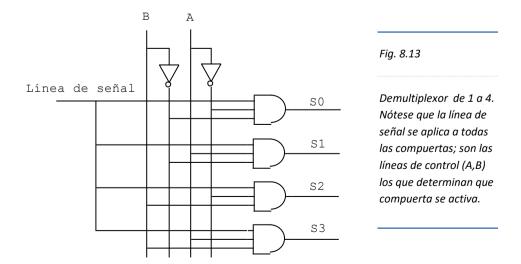

| 8.2.   |                                              | tiplexores                                                           | 186 |

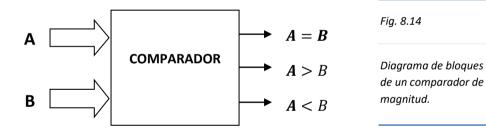

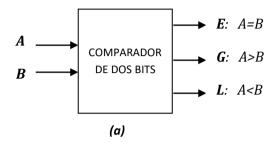

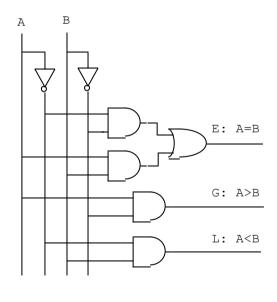

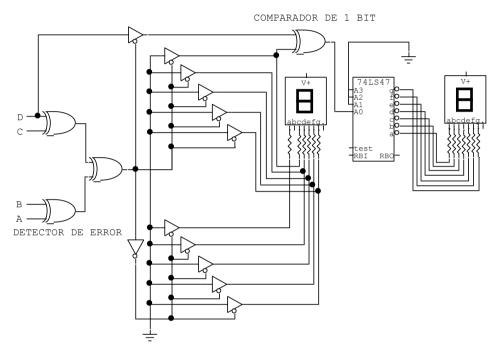

| 8.3.   | -                                            | radores de magnitud                                                  | 187 |

|        | 8.3.1.                                       | P                                                                    | 187 |

|        |                                              | entrada                                                              |     |

|        | 8.3.2.                                       | Diseño de un comparador de tres bits e datos en cada canal de        | 188 |

|        |                                              | entrada                                                              |     |

|        |                                              | sueltos № 08                                                         | 190 |

| Probl  | emas Pro                                     | opuestos № 08                                                        | 196 |

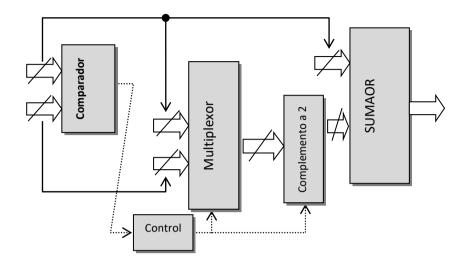

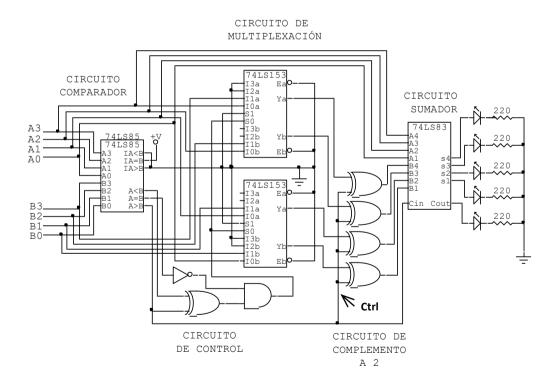

| Capíti | ulo 9: Cir                                   | rcuitos aritméticos                                                  |     |

| 9.1.   | Introdu                                      | ıcción                                                               | 199 |

| 9.2.   | Operac                                       | iones aritméticas                                                    | 200 |

|        | 9.2.1.                                       | Suma                                                                 | 200 |

|        | 9.2.2.                                       | Resta                                                                | 201 |

|        | 9.2.3.                                       | Multiplicación                                                       | 202 |

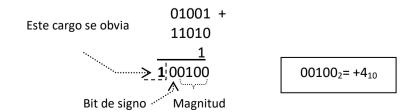

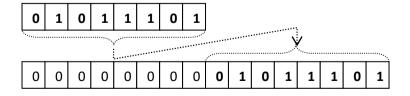

| 9.3.   | Repres                                       | entación de números con signo                                        | 203 |

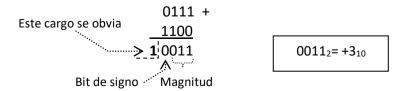

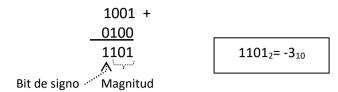

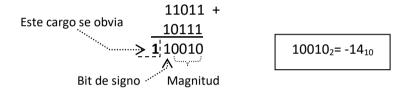

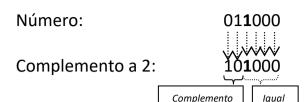

| 9.4.   | Sistema                                      | a de complemento a 2                                                 | 204 |

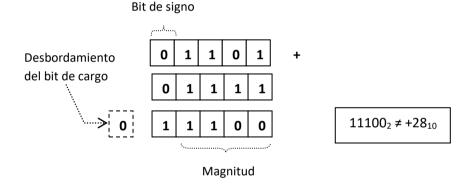

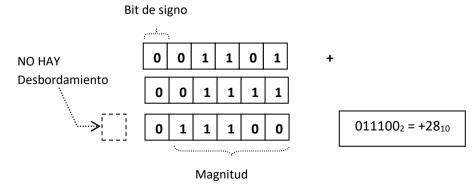

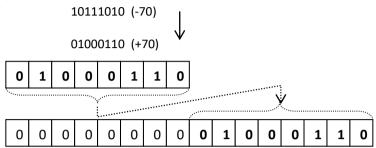

| 9.5.   | Operaciones en el sistema de complemento a 2 |                                                                      | 206 |

|        | 9.5.1.                                       | Suma en complemento a 2                                              | 206 |

|        | 9.5.2.                                       | Resta en complemento a 2                                             | 207 |

|        | 9.5.3.                                       | Desbordamiento aritmético                                            | 208 |

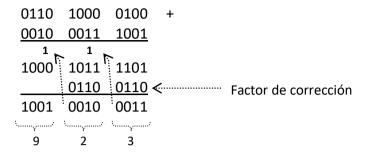

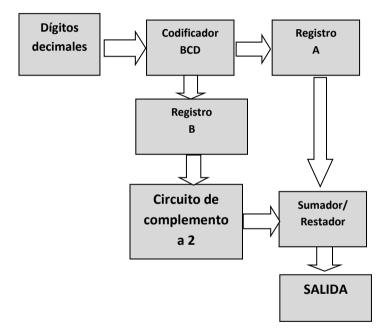

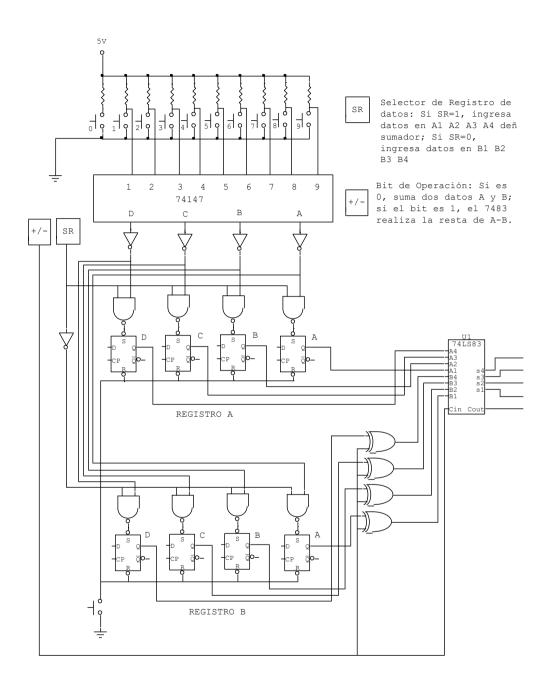

| 9.6.   | Suma B                                       | SCD                                                                  | 209 |

| 9.7.   | Sumado                                       | or digital                                                           | 210 |

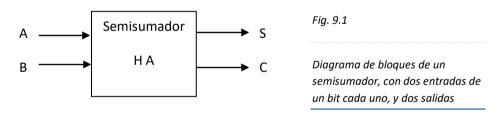

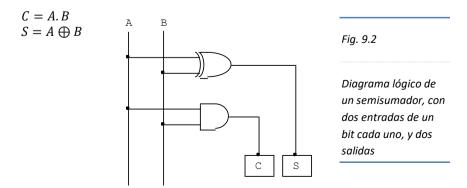

|        | 9.7.1.                                       | Semisumador                                                          | 210 |

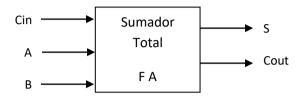

|        | 9.7.2.                                       | Sumador total                                                        | 211 |

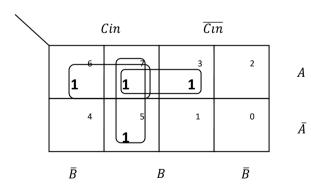

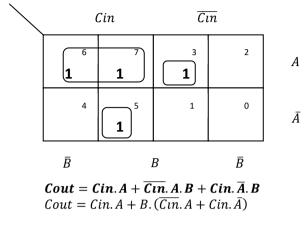

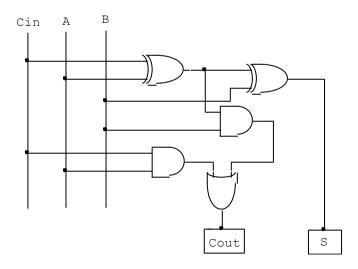

|        | 9.7.3.                          | Diseño de un sumador total                            | 213 |  |

|--------|---------------------------------|-------------------------------------------------------|-----|--|

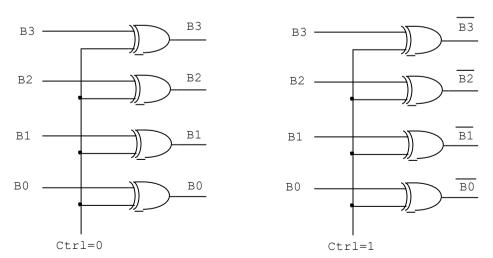

|        | 9.7.4.                          | Circuitos restadores                                  | 213 |  |

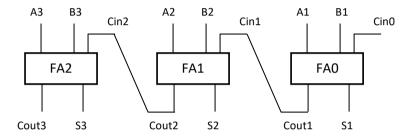

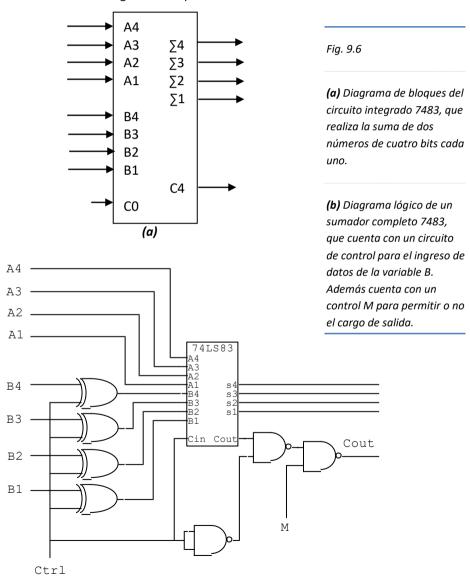

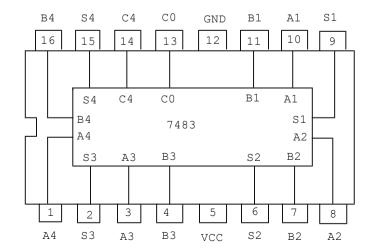

| 9.8. B | loques s                        | umadores prácticos de 4 bits de datos                 | 214 |  |

| Probl  | emas Re                         | sueltos № 09                                          | 216 |  |

| Probl  | emas Pro                        | opuestos Nº 09                                        | 222 |  |

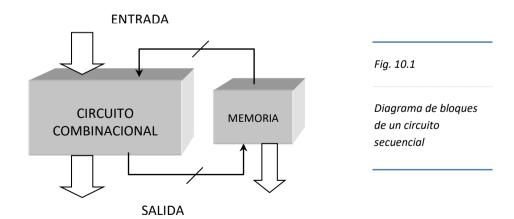

| Capít  | ulo 10: C                       | ircuitos secuenciales                                 |     |  |

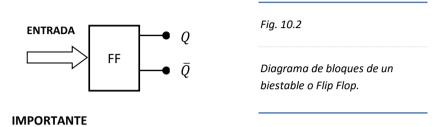

| 10.1.  | Introdu                         | cción a los circuitos secuenciales                    | 223 |  |

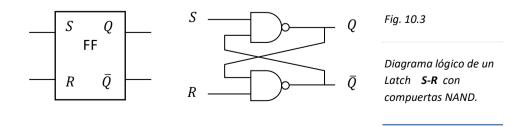

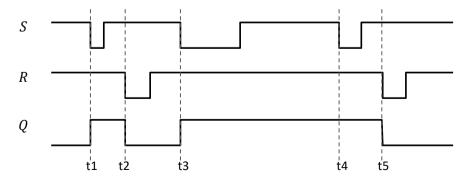

| 10.2.  | Flip Flo                        | p SR                                                  | 224 |  |

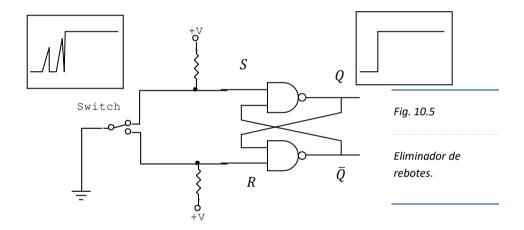

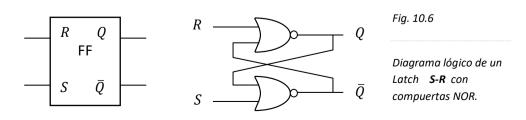

|        | 10.2.1.                         | Latch de compuertas NAND                              | 224 |  |

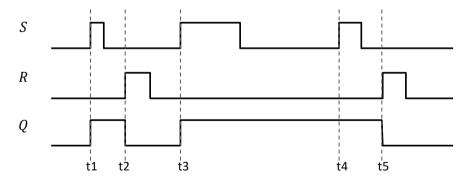

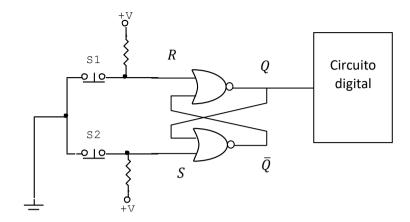

|        | 10.2.2.                         | Latch de compuertas NOR                               | 226 |  |

| 10.3.  |                                 | ización de los biestables                             | 229 |  |

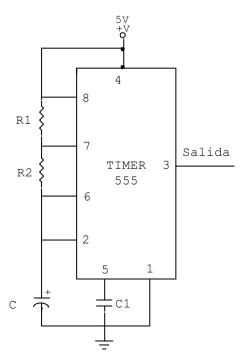

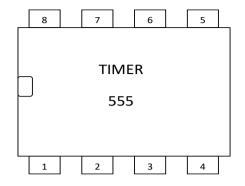

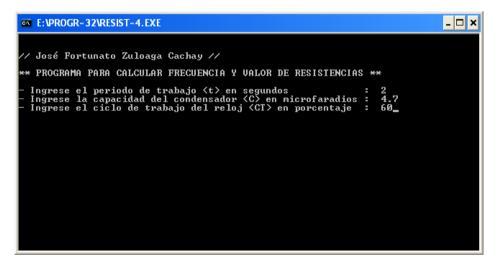

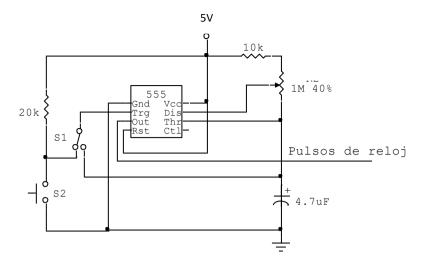

|        | 10.3.1.                         | Circuito generador de reloj                           | 229 |  |

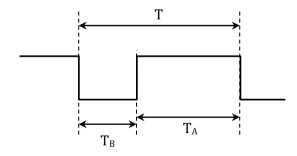

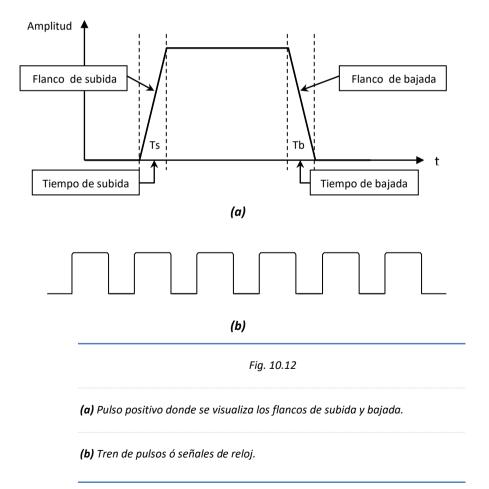

|        | 10.3.2.                         | Pulsos digitales                                      | 232 |  |

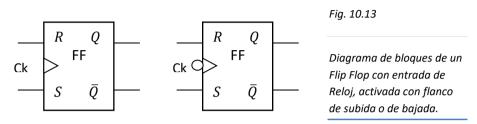

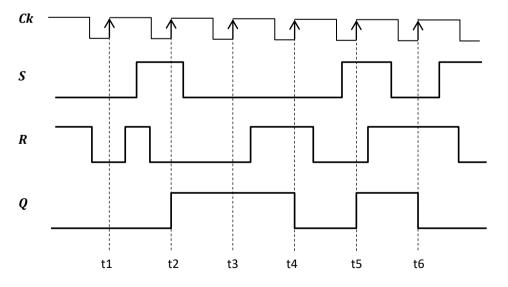

|        | 10.3.3.                         | Flip Flop S-R sincronizados por reloj                 | 233 |  |

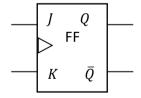

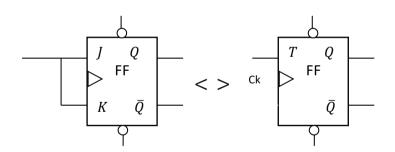

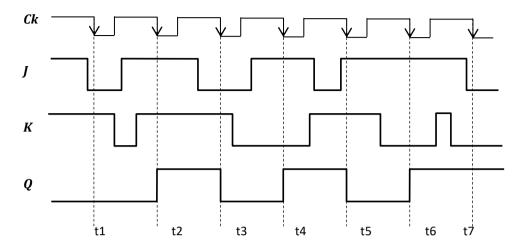

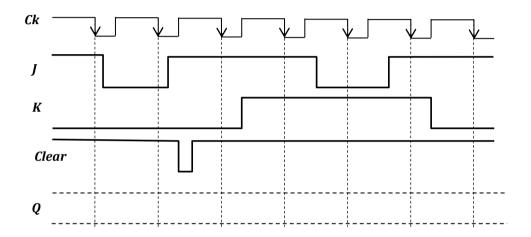

| 10.4.  | Flip Flo                        |                                                       | 234 |  |

|        |                                 | FF JK Master Slave                                    | 234 |  |

|        |                                 | FF JK edge – triggered                                | 235 |  |

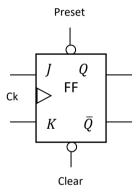

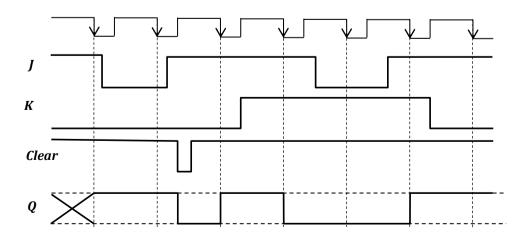

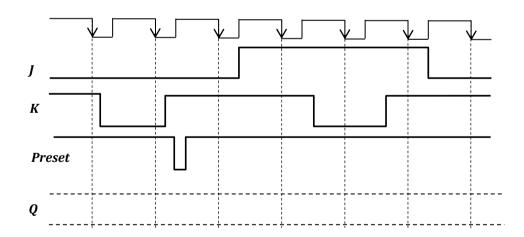

|        |                                 | Entradas asíncronas en el FF JK                       | 235 |  |

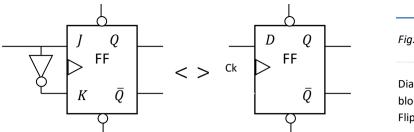

|        | Flip Flo                        |                                                       | 235 |  |

|        | Flip Flo                        |                                                       | 236 |  |

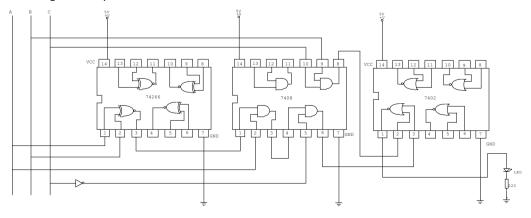

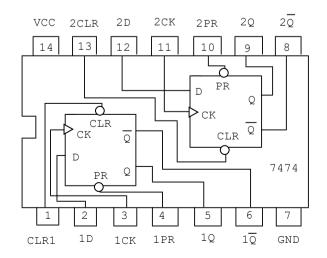

|        |                                 | os integrados comerciales de Flip Flop                | 237 |  |

|        |                                 | sueltos № 10                                          | 238 |  |

| Probl  | emas Pro                        | opuestos № 10                                         | 242 |  |

| Capít  | ulo 11: A                       | lmacenamiento y transferencia de datos                |     |  |

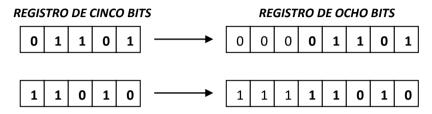

| 11.1.  | Registro                        | OS                                                    | 243 |  |

| 11.2.  | Registros de desplazamiento     |                                                       |     |  |

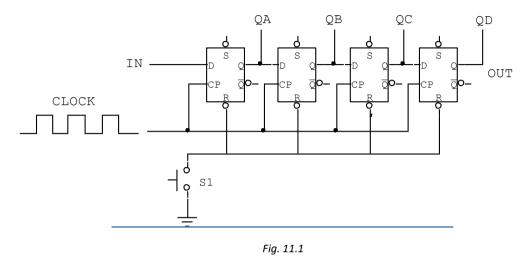

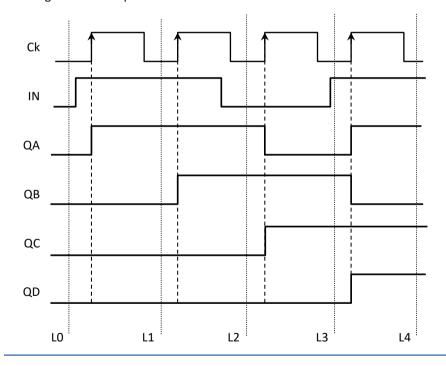

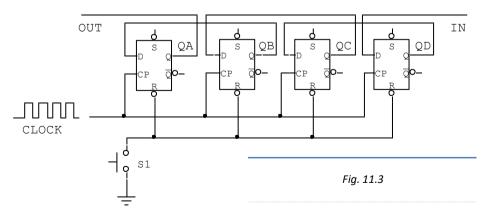

|        | 11.2.1.                         | Registro de desplazamiento: entrada y salida en serie | 244 |  |

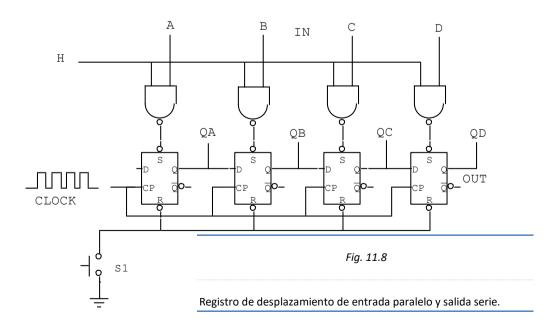

|        |                                 | Registro de entrada paralelo y salida serie           | 251 |  |

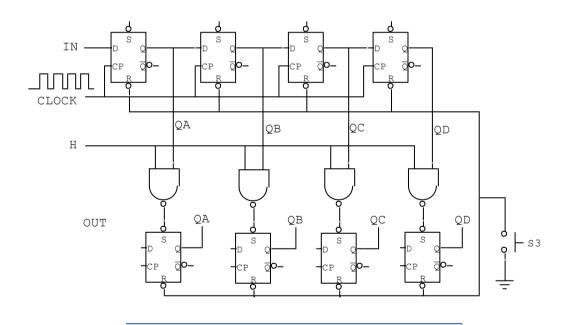

|        | 11.2.3.                         | Registro de entrada serie y salida paralelo           | 252 |  |

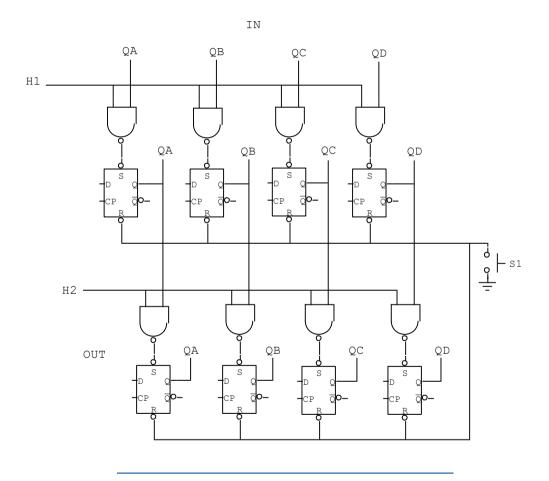

|        |                                 | Registro de entrada paralelo y salida paralelo        | 253 |  |

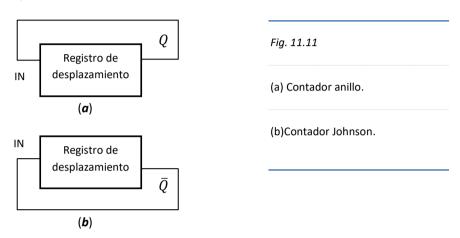

|        | _                               | o de desplazamiento en lazo cerrado                   | 254 |  |

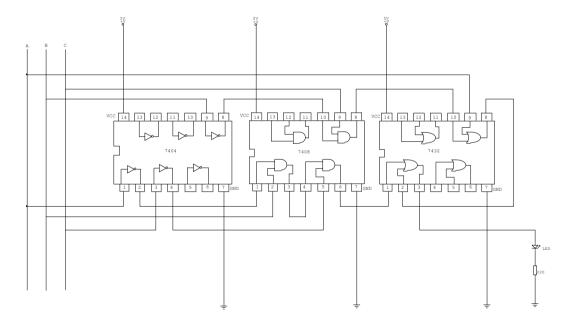

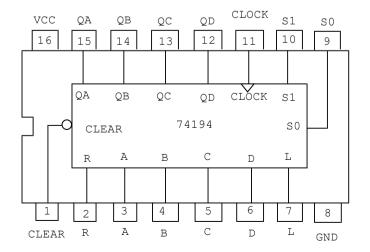

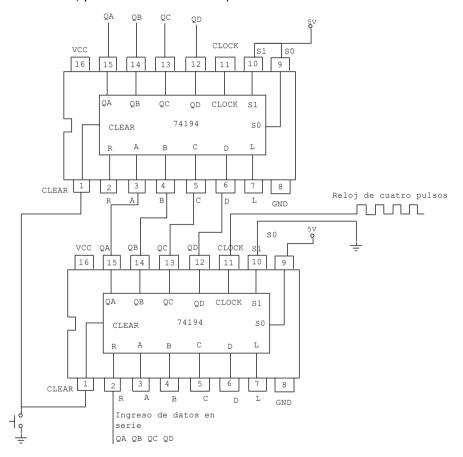

|        | _                               | os comerciales 74164, 74165, 74166, 74194             | 255 |  |

|        | Bus de                          |                                                       | 256 |  |

|        |                                 | sueltos № 11                                          | 257 |  |

| Probl  | emas Pro                        | opuestos № 11                                         | 259 |  |

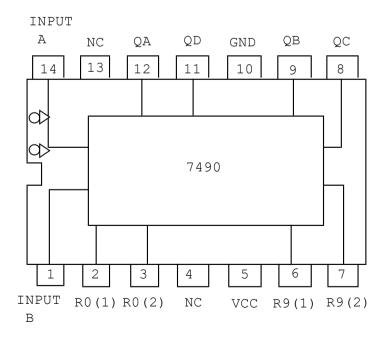

| Capít  | ulo 12: C                       | ontadores                                             |     |  |

| 12.1.  | . Introducción                  |                                                       |     |  |

| 12.2.  | Clasificación de los contadores |                                                       |     |  |

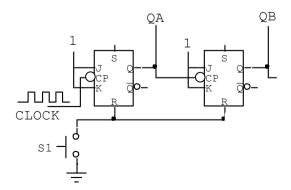

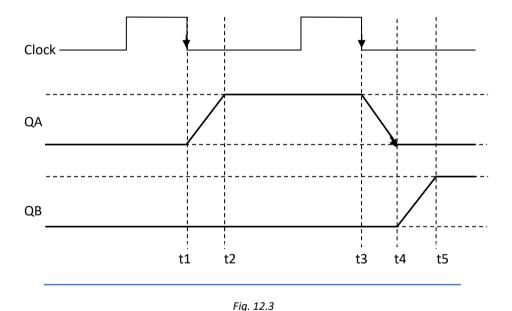

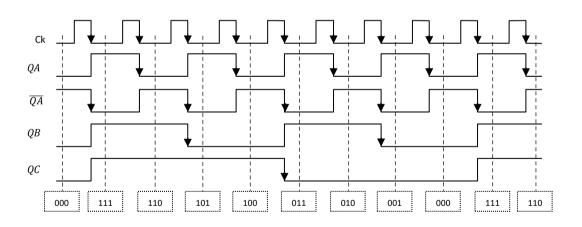

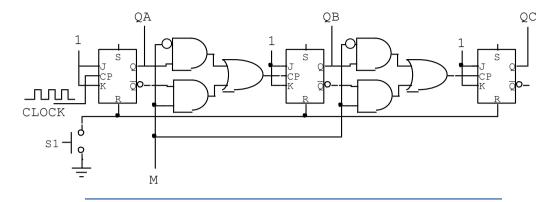

|        | 12.2.1.                         | Contadores asíncronos de rizo                         | 262 |  |

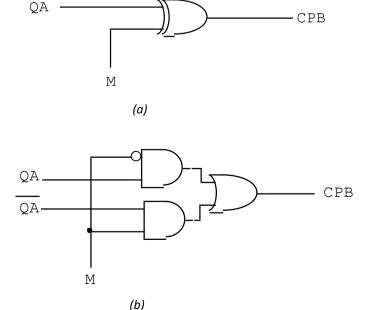

|        |                                 | 12.2.1.1. Contador asíncrono ascendente               | 265 |  |

|        |                                 | 12.2.1.2. Contador asíncrono descendente              | 266 |  |

|        |                                 | 12.2.1.3. Contador Módulo N                           | 269 |  |

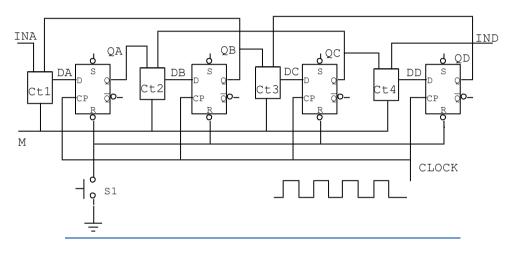

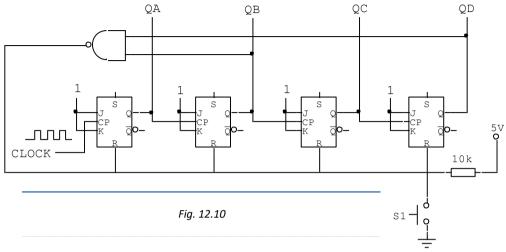

|        | 12.2.2. Contado |              | es síncronos                                      | 270 |

|--------|-----------------|--------------|---------------------------------------------------|-----|

|        |                 | 12.2.2.1.    | Contador síncrono binario                         | 270 |

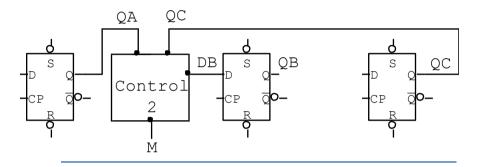

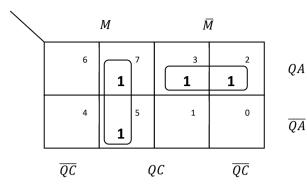

|        |                 | 12.2.2.2.    | Contador década síncrono                          | 273 |

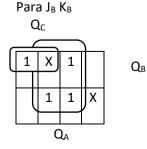

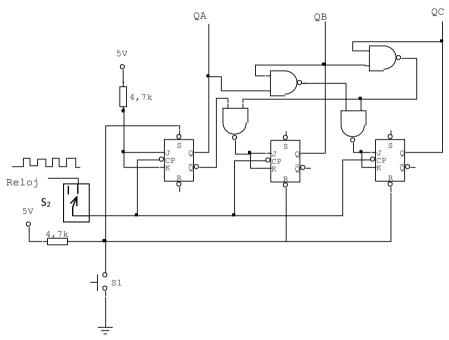

|        |                 | 12.2.2.3.    | Diseño de contadores síncronos utilizando las     |     |

|        |                 |              | entradas del Flip Flop JK de manera independiente | 275 |

|        |                 | 12.2.2.4.    | Contador escalonador                              | 276 |

| Proble | emas Res        | sueltos Nº   | 12                                                | 277 |

| Proble | emas Pro        | puestos N    | 2 12                                              | 283 |

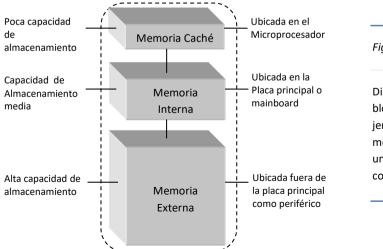

| Capítı | ulo 13: D       | ispositivos  | de memoria                                        |     |

| -      | Memor           | -            |                                                   | 285 |

|        |                 | rísticas gei | nerales                                           | 286 |

|        |                 | ón de la me  |                                                   | 286 |

| 13.4.  | Clases o        | de memoria   | a                                                 | 287 |

|        | 13.4.1.         | Memoria      | s de semiconductores                              | 287 |

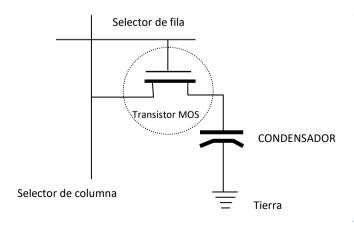

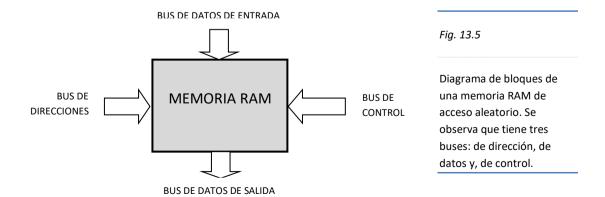

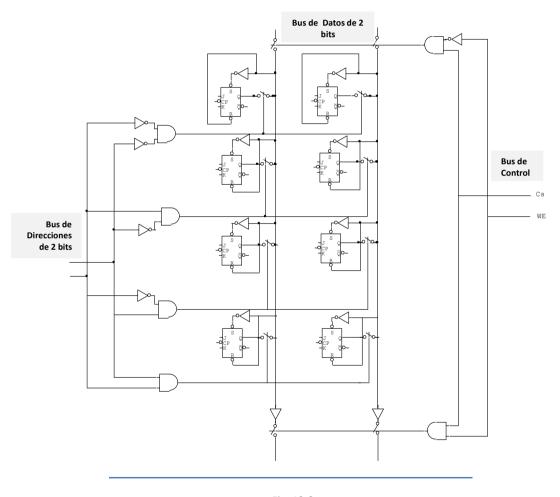

|        |                 | 13.4.1.1.    | Memorias de acceso aleatorio (RAM)                | 287 |

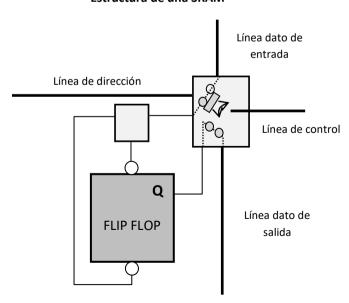

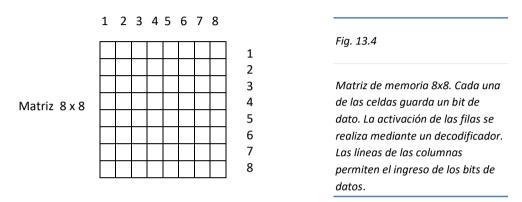

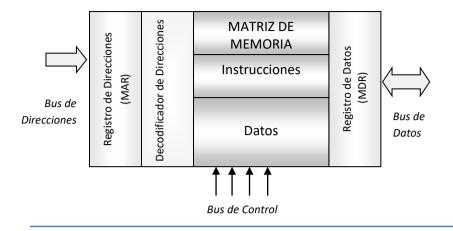

|        |                 | 13.4.1.2.    | Matriz de memoria semiconductora básica           | 290 |

|        |                 | 13.4.1.3.    | Estructura de una RAM semiconductora              | 290 |

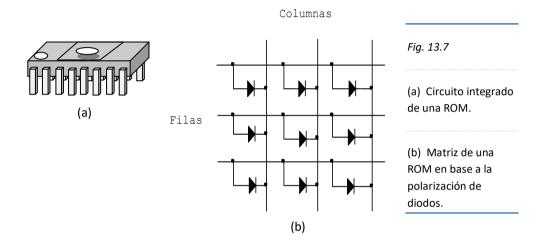

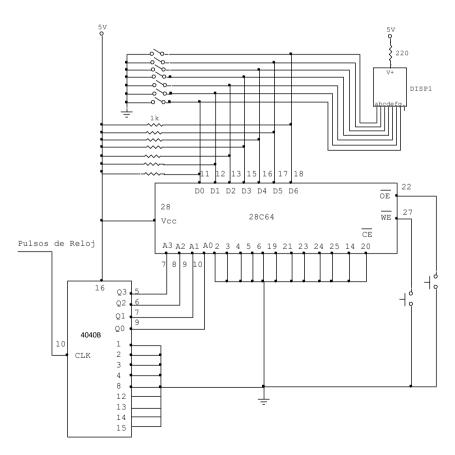

|        |                 | 13.4.1.4.    | Memorias de solo lectura (ROM)                    | 292 |

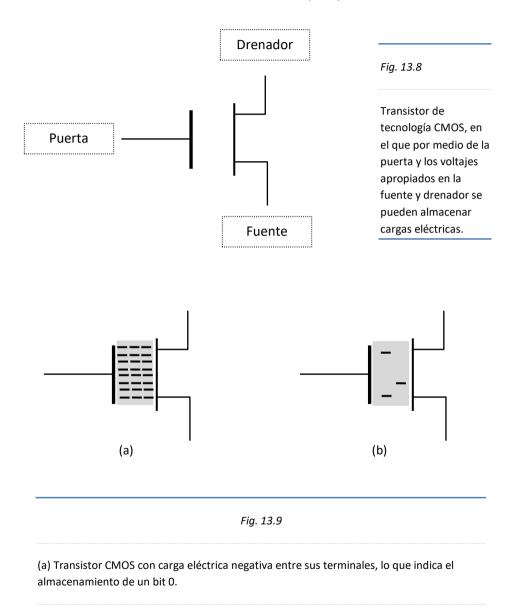

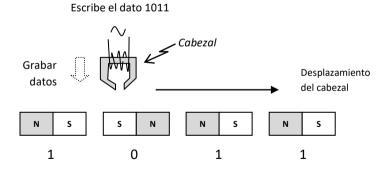

|        |                 | 13.4.1.5.    | Memorias Flash                                    | 293 |

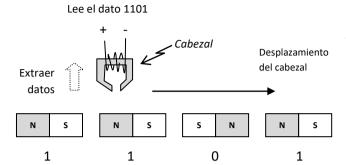

|        | 13.4.2.         | Memoria      | s magnéticas                                      | 295 |

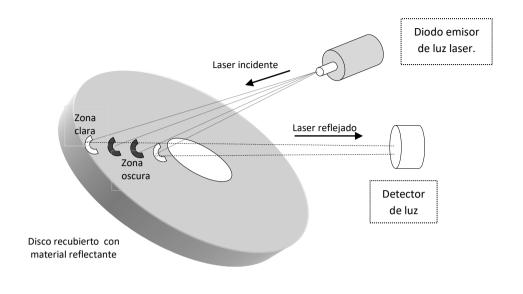

|        | 13.4.3.         | Memoria      | s ópticas                                         | 296 |

| 13.5.  | Distril         | bución inte  | erna de la memoria                                | 297 |

| Proble | emas Res        | sueltos Nº   | 13                                                | 298 |

| Proble | emas Pro        | puestos N    | 2 13                                              | 300 |

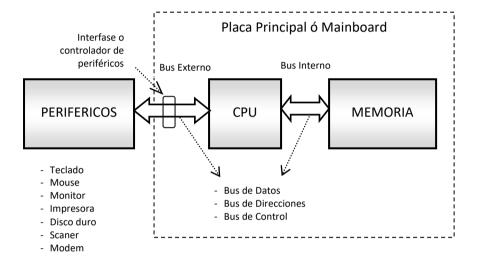

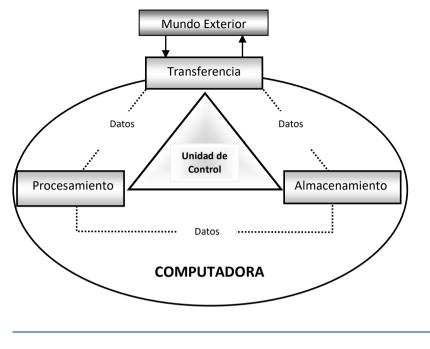

| Capítı | ulo 14: Es      | structura b  | ásica de un computador                            |     |

| 14.1.  | El comp         | outador      |                                                   | 301 |

| 14.2.  | Organiz         | ación y arc  | quitectura                                        | 302 |

| 14.3.  | Estructi        | ura y funcio | ón                                                | 302 |

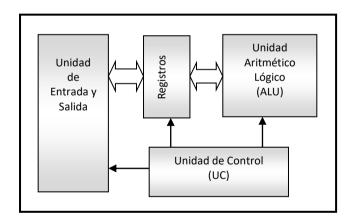

| 14.4.  | El micro        | procesado    | or                                                | 304 |

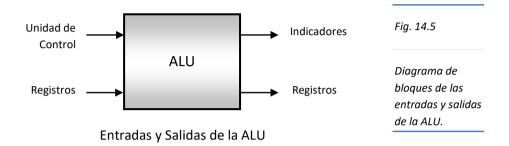

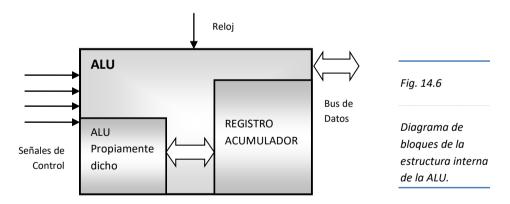

|        | 14.4.1.         | Unidad A     | ritmético lógica                                  | 305 |

|        | 14.4.2.         | Registro t   | temporal de almacenamiento de datos y direcciones | 307 |

|        |                 | 14.4.2.1.    | Registros visibles al usuario                     | 307 |

|        |                 | 14.4.2.2.    | Registros de control y de estado                  | 307 |

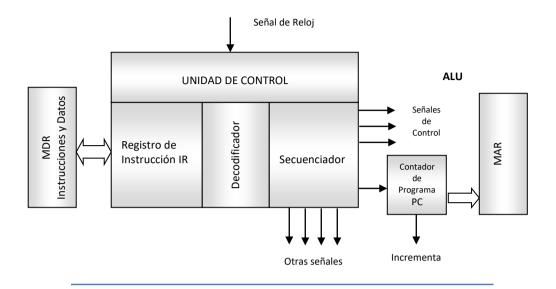

|        | 14.4.3.         | Unidad d     | e Control                                         | 307 |

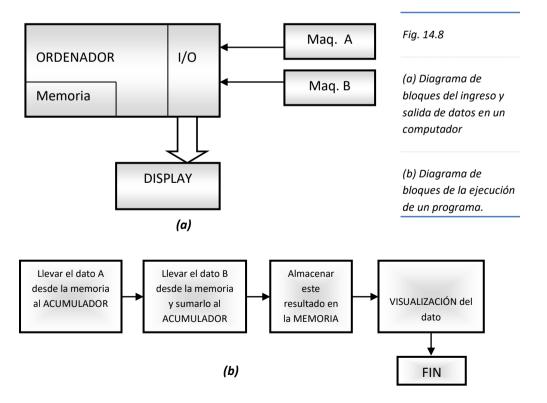

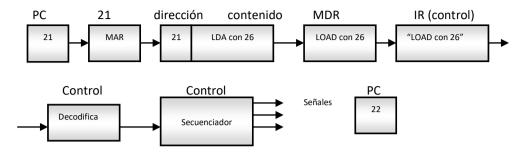

| 14.5.  | Funcion         | namiento d   | el computador                                     | 308 |

| Biblio | grafía          |              |                                                   | 313 |

## Introducción

l desarrollo vertiginoso de los sistemas computacionales a revolucionado el mundo, pues, desde los artefactos domésticos más sencillos, hasta los más avanzados aparatos de comunicación y equipos de control, cuentan con dispositivos y componentes electrónicos digitales que posibilitan un adecuado manejo y procesamiento de señales basados en niveles lógicos.

Las computadoras personales y los sistemas digitales en general poseen circuitos secuenciales provistos de memoria, en los cuales es común almacenar algún tipo de software que facilita el gobierno de los diversos componentes del que dispone.

Aunque el funcionamiento interno de todos los aparatos digitales es transparente a la mayoría de las personas que las manipulan, es necesario que consideremos la posibilidad de interesarnos cada vez más en comprender el funcionamiento de dichos artefactos, habida cuenta que la aparición de esta tecnología ha venido para quedarse con nosotros.

Los estudiantes de las carreras profesionales de ingeniería de sistemas, así como los de computación e informática, tienen a los diversos sistemas computacionales como herramienta de trabajo, por lo que es necesario que comprendan y dominen las más básicas y avanzadas técnicas digitales para que su desempeño profesional se perfeccione cada vez más y su trabajo se optimice en este mundo tan competitivo.

Este libro tiene como propósito facilitar las ideas básicas, así como los principios y técnicas digitales en un nivel básico e intermedio, que posibilite a quien lo lea y practique, adquirir destrezas y habilidades en el análisis y

diseño de circuitos combinacionales y secuenciales, conocimientos que son la base para incursionar en el mundo de los microcontroladores y para comprender la arquitectura y el funcionamiento de las computadoras personales.

Asimismo, es preciso aclarar que en nuestro medio existe una variedad de textos de muy alto nivel académico en electrónica digital, que obviamente está destinado para aquellas personas que desean especializarse en sistemas digitales. No obstante, es conveniente precisar que en el texto de "Electrónica Digital para Arquitectura de Computadoras" se encontrará la mayoría de los temas tratados en las currículas profesionales de las universidades e institutos de educación superior de nuestro medio, los cuales están expuestos de una manera sencilla y didáctica.

El presente texto está estructurado en catorce capítulos y distribuidos en tres bloques y un capítulo final donde se muestra la estructura básica de un computador personal.

El capítulo 1 expone los fundamentos de la electrónica analógica que son la base para estudiar los circuitos y componentes digitales.

Del capítulo 2 al capítulo 9 se trata todo lo relacionado con los circuitos combinacionales, en ellos, se estudian los sistemas de numeración binario, el álgebra de Boole, métodos de simplificación, codificadores, multiplexores, decodificadores, demultiplexores, comparadores y circuitos aritméticos.

Del capítulo 10 al capítulo 13 se analizan los circuitos secuenciales, los cuales utilizan un sistema generador de reloj para secuenciar sus principales funciones, como son los Flip Flops, Registros, contadores y memorias.

El capítulo 14 presenta la arquitectura básica de un sistema computacional.

Los contenidos tratados en el presente texto, puede desarrollarse convenientemente en un semestre académico, asimismo, por las características de su estructura y desarrollo de los temas, puede ser utilizado por aquellas personas autodidactas o que realizan estudios profesionales a distancia, afianzando sus conocimientos con un conjunto de ejercicios y problemas resueltos y propuestos.

Autores.

### Capítulo 1

## Fundamentos de Electrónica Analógica

#### 1.1. Magnitudes eléctricas

Las magnitudes eléctricas son todas aquellas cantidades que describen cuantitativamente a los circuitos eléctricos y electrónicos. Las más importantes son: la carga, corriente, voltaje, potencia y energía eléctrica.

#### 1.1.1. Carga eléctrica

Es la propiedad física que poseen los electrones y los protones. Todos los cuerpos pueden cargarse eléctricamente, unos más que otros, pero cuando un cuerpo posee igual cantidad de cargas negativas y positivas se dice que dicho cuerpo es eléctricamente neutro. Cuando hay un desbalance en las cargas eléctricas, se dice que los cuerpos son *negativos* si hay mayor cantidad de electrones y, *positivos* si tienen mayor cantidad de protones o menor cantidad de electrones. La interacción entre los cuerpos electrizados se manifiesta en la repulsión de cargas iguales o la atracción de cargas opuestas.

La unidad de medida de la carga eléctrica (Q) es el coulomb (C), el cual es equivalente a la electricidad de 6,25 x  $10^{18}$  electrones.

La carga eléctrica del electrón es -1,602 x 10<sup>-19</sup> C.

Las impresoras de tecnología láser utilizan la propiedad de las cargas eléctricas para imprimir documentos. El proceso de impresión lo realiza una luz láser del sistema óptico de la impresora, esta luz incide sobre un tambor del cartucho de tóner. La parte del tambor iluminada por el láser se carga eléctricamente y atrae partículas de tóner cargadas con carga eléctrica opuesta al tambor. El papel pasa por el tambor y luego a un mecanismo de fijación en el que se calienta y fija el tóner.

El cuerpo humano también se carga eléctricamente, ya sea por el

rozamiento con el aire o nuestras prendas de vestir. A ésta acumulación de cargas se le llama "cargas electrostáticas". Ésta electricidad imperceptible para nosotros puede dañar fácilmente a dispositivos electrónicos de tecnología MOSFET.

Para evitar daños en componentes de una computadora por efecto de una descarga electrostática (ESD), es necesario que realicemos un proceso de descarga utilizando el sistema de Tierra, o simplemente tocando por breves segundos cualquier material metálico que haga contacto con Tierra.

#### 1.1.2. Corriente eléctrica

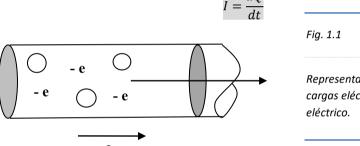

La *corriente eléctrica* (*I*) se define como el flujo de *cargas eléctricas* (*Q*) que atraviesan la sección de un conductor eléctrico en un determinado *tiempo* (*t*).

Representación del movimiento de cargas eléctricas en un conductor eléctrico

El movimiento de los electrones libres en un conductor produce el flujo de cargas en un sentido, como I en la Fig. 1-1; podemos decir que en el sentido contrario circulan cargas positivas. Convencionalmente, el sentido de la corriente electrónica es opuesto al sentido del movimiento de los electrones.

La unidad de medida de la corriente eléctrica es el *Amperio* (A), donde:

$$1A = \frac{1C}{s}$$

Un Amperio (A) es equivalente a la circulación de un coulomb (C) o 6,25 x  $10^{18}$  electrones en un segundo.

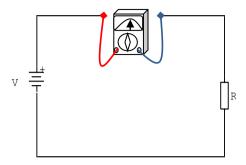

El instrumento de medida de la corriente eléctrica es el *amperímetro*<sup>1</sup>. Éste instrumento se instala en serie con el circuito tal como se muestra en la Fig. 1.2.

<sup>&</sup>lt;sup>1</sup> El *amperímetro*, el *voltímetro* y el *ohmímetro* se hallan en un solo instrumento llamado **multímetro** o **multiteste**r.

Fig.1.2

Para medir la corriente eléctrica, el amperímetro se instala en serie con el circuito.

Los efectos de la corriente eléctrica cuando circula por el cuerpo humano están en función de la Intensidad de la corriente y el tiempo de aplicación. Cuando circula una corriente entre 1mA y 100mA, el organismo reacciona de distintas formas, desde temblores musculares hasta dolorosas contracciones y paro respiratorio. Si la intensidad de corriente es superior a 100mA es probable la muerte por arritmia cardiaca y quemaduras de primer y segundo grado.

Es preciso aclarar que la cantidad de corriente que puede circular por el organismo humano, depende de la resistencia eléctrica del mismo. A mayor resistencia del cuerpo, menor será la corriente que circule por el mismo.

La fuente de poder de una computadora proporciona suficiente corriente para que funcionen los dispositivos y componentes instalados. Por ejemplo, el cable rojo de la salida de la fuente de alimentación abastece con 50A, aproximadamente.

#### 1.1.3. Voltaje

El voltaje (V), denominado también tensión eléctrica o diferencia de potencial, se define básicamente como el efecto del trabajo (W) realizado por el campo eléctrico (E) sobre una carga eléctrica (Q); lo que en realidad viene a ser la variación de energía potencial eléctrico  $(\Delta U)$  por unidad de carga entre dos puntos de un campo eléctrico, es decir, el trabajo (W) es equivalente a la energía potencial  $(\Delta U)$ .

$$V = \frac{W}{Q} = \frac{\Delta U}{Q} = -E \cdot \Delta d$$

La unidad de medida del voltaje el voltio (V)

1 voltio (V) =

$$\frac{1 \text{ joulio (J)}}{\text{coulomb (C)}} = \left(\frac{1 \text{ newton (N)}}{\text{coulomb (C)}}\right) \times 1 \text{ metro (m)}$$

Nótese que la unidad de la energía potencial eléctrico ( $\Delta U$ ) es el **joulio (J)**.

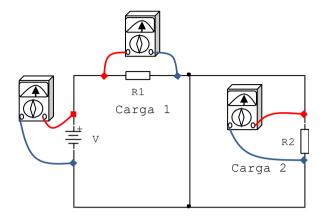

El instrumento de medida del voltaje es el *voltímetro*. Para medir el voltaje de una fuente de poder, o la caída de tensión en la carga de un circuito. El voltímetro

se instala en paralelo con el circuito, tal como se muestra en la Fig. 1.3.

Fig. 1.3

Instalación de un voltímetro en paralelo con los componentes en los que se desea saber su voltaje.

Las pilas, baterías y los generadores eléctricos, son fuentes de voltaje, pues internamente realizan trabajo para separar las cargas positivas de las negativas y así producir una diferencia de potencial que permitirá el flujo de corriente eléctrica en el interior de un circuito.

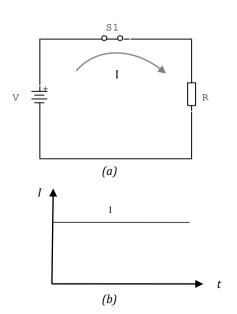

En general, hay dos clases de fuentes de voltajes: **continua** y **alterna**. La fuente de voltaje continua proporciona **corriente continua** o **directa** (c.d), a su vez, la fuente de voltaje alterna genera **corriente alterna** (c.a), tema que se tratará en (1.1.8 y 1.1.9).

El símbolo de la fuente de voltaje continua es

√ ‡

Fig. 1.4

- (a) Circuito serie cuya corriente circula del positivo de la fuente hacia el negativo, pasando por la resistencia.

- (b) Representación de la corriente continua que circula por un circuito eléctrico, sin cambiar de polaridad en el transcurso del tiempo.

El voltaje producido por las pilas, baterías y acumuladores suministra corriente directa (c.d) a un circuito eléctrico o electrónico, en función del tiempo de aplicación. A mayor tiempo de uso la diferencia de potencial entre sus bornes es cada vez menor. Se procede a cargarlos eléctricamente si son "recargables", sino, se reemplazan completamente por uno nuevo.

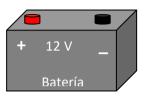

La batería de 12V y 50AH, es un acumulador de cargas eléctricas, recargable. Se utilizan en los (Ups) convertidores de 12V c.d a 220V de c.a, para proveer corriente alterna a los equipos de cómputo ante un eventual corte de energía de la red eléctrica y de ésta manera salvaguardar la "data" y los procesos informáticos que en

ese momento trabajaban.

El valor nominal de 50AH, indica que la batería puede proporcionar una corriente de 50 Amperios en una hora, o bien, 1 Amperio en 50 horas. Sin embargo, una computadora requiere más de 50 AH, lo que significa que los usuarios sólo dispondrán de aproximadamente 20 minutos para guardar la "data" y terminar el proceso con bastante seguridad.

Batería alcalina de 9V y 150mAH (miliamperio hora), dimensiones 17,5 x 26,5 x 48,5 mm; muy utilizado para la experimentación con circuitos digitales. Se utiliza un regulador de voltaje a 5V, y a éste voltaje se instalan circuitos integrados y demás componentes para comprobar algunas funciones lógicas o el diseño de circuitos electrónicos.

Las placas principales o mainboard de las computadoras disponen de una batería de 3V, en especial del modelo CR-2032. Se trata de una pila de litio, tipo botón, de larga duración. Provee de energía a una memoria del tipo CMOS.

#### 1.1.4. Ley de Ohm

La ley de Ohm establece una relación entre el voltaje, la corriente y la resistencia eléctrica (R). Cuando la resistencia (R) es constante, el voltaje (V) es directamente proporcional a la corriente eléctrica (I); esto es, a mayor voltaje, circulará mayor corriente por el circuito.

$$V = I \times R$$

Si deseamos que más corriente circule por un circuito serie como el de la Fig. 1.4 (a), deberíamos bajar la resistencia (R) y mantener constante el voltaje de la fuente de alimentación. Para realizar ésta operación se deberá tener en cuenta la potencia eléctrica de la fuente.

#### 1.1.5. Resistencia Eléctrica

La resistencia eléctrica (R) se define como la oposición que ofrece un conductor al paso de la corriente eléctrica.

La resistencia (R) de un conductor se halla dividiendo el voltaje entre la corriente.

$$R = \frac{V}{I}$$

; Resistencia =  $\frac{Voltaje}{Corriente}$

La unidad de medida de la resistencia eléctrica (R), es el Ohmio  $(\Omega)$ .

$$1 \ Ohmio = \frac{1 \ Voltio}{1 \ Amperio}$$

Es decir, si se aplica un voltaje de 10V a un conductor y por él circula una corriente de 2A, entonces, éste conductor tendrá una resistencia de  $5\Omega$ .

El símbolo de la resistencia eléctrica es una línea quebrada en la simbología americana, mientras que en la europea, es un rectángulo.

El instrumento de medida de la resistencia eléctrica (R), es el **ohmímetro**.

Para medir la resistencia de un resistor, el ohmímetro se conecta en paralelo, es decir, se conectan cada punta de medida del instrumento a los extremos del dispositivo.

Si el resistor se localiza el interior de un circuito eléctrico, es necesario desconectar previamente la fuente de voltaje.

Los resistores, son dispositivos que presentan una determinada resistencia al paso de la corriente eléctrica. El valor de resistencia de cada uno de ellos se establece según unas franjas de colores en su superficie y leídos según un código de colores.

Todos los componentes de un sistema de cómputo: fuentes de poder, placa principal, discos duros, monitores, impresoras, etc., incorporan en sus circuitos, en su mayoría, resistores de carbón.

#### 1.1.6. Potencia eléctrica

La potencia eléctrica (P) de una fuente de energía, es la rapidez con el que transfiere energía potencial eléctrica a un dispositivo determinado.

$$P = \frac{dU}{dt} = d\frac{(QV)}{dt} = \frac{dQ}{dt} \times V$$

La *potencia eléctrica (P)*, se puede definir como el producto de la *corriente (I)* por el *voltaje (V)*.

$$P = I \times V$$

La unidad de medida de la potencia eléctrica, es el watt (W).

$$1 watt = \frac{1 joulio}{segundo} = 1 amperio \times voltio$$

El instrumento de medida de la potencia eléctrica es el **wattimetro**. Aunque en electrónica no es común el uso de éste instrumento, en caso se requiera, se puede utilizar un **amperímetro** y un **voltímetro** simultáneamente, y con los valores obtenidos se calcula la potencia del circuito.

Todos los equipos electrónicos obtienen energía eléctrica de una fuente de poder o fuente de alimentación, el cual provee de potencia eléctrica a los dispositivos y componentes del circuito, es decir, le suministra corriente y voltaje.

Un monitor LCD (pantalla de cristal líquido) de 17" consume 35W, mientras que uno TRC (tubo de rayos catódicos), requiere 80W.

Una impresora común de inyección de tinta, funciona con una fuente de alimentación de 12W de potencia, con una salida de 30V y 400mA.

Una computadora actual funciona con una fuente de poder de 600W, mientras que las más antiguas funcionaban correctamente con 150W y 200W; pero, cada vez que el sistema computacional evoluciona y nos procura mejores prestaciones, requiere a cambio, cada vez más potencia.

Aunque el voltaje no varía, sí lo hace la corriente. Si una fuente de 150W aportaba 20A en el cable rojo de 5V; una fuente de 600W provee 50A en el mismo terminal.

Los estabilizadores de voltaje, en los cuales se instalan las computadoras, disponen de potencia que varía según el fabricante y modelo, que van desde  $600\,W$  a más de  $2\,000\,W$  o  $2\,KW$ .

#### 1.1.7. Energía y potencia

Es importante comprender la diferencia entre la energía y la potencia eléctrica. Ambas magnitudes están relacionadas de tal manera que la **energía** (W) es directamente proporcional a la **potencia** (P) y al **tiempo** (t) de uso.

$$W = P \times t$$

Cuando la empresa proveedora de energía eléctrica emite un recibo por consumo mensual, lo hace tomando en cuenta el consumo de energía eléctrica y no de la potencia disponible.

Esto quiere decir que el consumo de energía de la fuente de poder de un artefacto con una determinada potencia, será mayor cuanto más tiempo se use dicho artefacto.

La unidad de medida de la energía consumida es el *Watt-segundo (W.s)*. Sin embargo, para cuestiones prácticas, ésta cantidad es demasiado pequeña, es por ello que se utiliza la unidad *Watt-hora (W.h)* ó el *Kilowatt-hora (KW.h.*)

$$Kilowatt.hora = \frac{Pt}{1000}$$

Si en un día promedio, utilizamos la computadora de (500W) durante 5 horas ¿Cuál será el consumo de energía en un mes?

Consumo de energía diario =

$$\frac{500 \times 5}{1000}$$

= 2,5 KW.h

Consumo de energía mensual =  $2,5 \, KW. \, h \times 30 = 75 \, KW. \, h$

Tómese en cuenta a modo de referencia el consumo energético que realiza un foco de filamento incandescente de 100W, y téngase presente que el consumo de energía de cada uno de los equipos utilizados es acumulativo.

#### 1.1.8. Corriente Alterna

Cuando deseamos trabajar con una computadora y todos sus periféricos, los conectamos o instalamos al tomacorriente, del cual obtenemos la energía necesaria para su funcionamiento.

Cuando la corriente es alterna, significa que el sentido de la corriente se invierte periódicamente. Si la corriente es alterna, el voltaje también es alterno, lo que quiere decir, que está variando con el tiempo.

Algunos países como el nuestro utilizan 220V de corriente alterna, mientras

que otros han adoptado 110V, para los mismos propósitos. Las empresas proveedoras de energía eléctrica, nos proporcionan corriente alterna a través de una red eléctrica normalmente trifásica.

La vivienda en su gran mayoría recibe energía eléctrica a través de una red eléctrica monofásica (usa sola fase), sin embargo, las empresas e industrias cuentan con un sistema trifásico, puesto que sus equipos y motores eléctricos funcionan con tres fases.

La corriente alterna a diferencia de la continua, presenta la capacidad de ser transportado a grandes distancias, desde los centros generadores hasta las ciudades o industrias, a través de cables de alta tensión y baja corriente, con la finalidad de reducir las pérdidas de energía por el efecto Joule.

#### 1.1.9. Generación de corriente alterna

La generación de corriente alterna se realiza mediante un dispositivo llamado "generador", cuyo atributo es convertir energía mecánica en energía eléctrica, aprovechando el fenómeno de inducción electromagnética.

La inducción electromagnética se presenta cuando un conductor en forma de espira gira en el interior de un campo magnético uniforme, creándose una *fuerza electromotriz* o *diferencia de potencial* en los extremos del conductor, el cual varía o se alterna en el tiempo. El mismo efecto se produce si un campo magnético uniforme gira alrededor de la espira.

El movimiento de la espira lo produce una central hidroeléctrica, térmica, eólica, o nuclear.

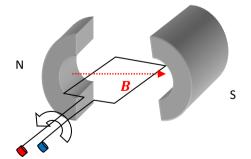

Fig.1.5

Movimiento de una espira en el interior de un campo magnético uniforme.

Cuando la espira gira, la corriente y el voltaje inducido en sus extremos varían tanto en magnitud como en dirección. Una rotación completa de la espira origina un ciclo completo del voltaje y de la corriente. La representación gráfica de este movimiento es una onda sinusoidal, con amplitud máxima cuando el plano de la espira está en paralelo con el campo magnético, y nula, cuando es perpendicular.

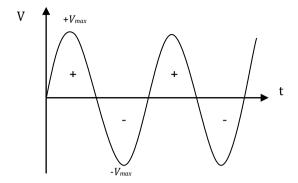

Fig.1.6

Onda sinusoidal que representa la alternancia de la polaridad del voltaje.

#### 1.1.10. Valores típicos de una señal alterna

Una señal alterna presenta valores característicos según la amplitud de la onda y el número de ciclos que realiza la espira por unidad de tiempo.

La fuerza electromotriz (fem) o voltaje alterna (V), en los extremos de la espira, se calcula según la siguiente relación.

$$V = V_{max} sen 2\pi f t$$

#### 1.1.10.1. Frecuencia

La frecuencia (f) de una señal alterna, es la cantidad que indica el número de ciclos por segundo que efectúa una espira al girar en el interior de un campo magnético.

La unidad de medida de la frecuencia es el *hertz (Hz)*. El instrumento de medida es el *frecuencímetro*.

La red eléctrica domiciliaria e industrial es de 60 Hz, esto quiere decir, que la espira ha rotado 60 veces en un segundo.

En general, la frecuencia está en relación inversa con el *periodo* (t).

$$f = \frac{1}{t}$$

En algunos circuitos digitales, especialmente en el generador de pulsos de reloj, se emplea la noción de frecuencia para diseñar e implementar contadores, registros y otros dispositivos secuenciales.

La velocidad del microprocesador, también se expresa en unidades de frecuencia, aunque en este caso, la velocidad se define como el número de ciclos por

segundo, una instrucción puede ser procesada en uno o varios segundos. Un valor típico de velocidad de un microprocesador actual es 3 GHz (Gigahertz) ó 3x10<sup>9</sup> Hz.

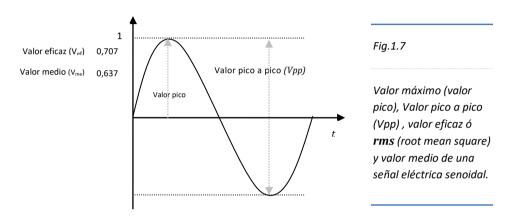

#### 1.1.10.2. Valor eficaz y valor medio

El Valor eficaz ( $V_{ef}$ ) o **rms** (raíz media cuadrática) de una señal alterna, es aquella corriente senoidal que produce el mismo efecto calórico al circular por una carga óhmica, que si circulara por ella una corriente continua equivalente.

Los valores máximos son aquellos valores de voltajes y corrientes instantáneos, que se dan en determinados momentos, sin embargo, los equipos que funcionan con corriente eléctrica alterna, no trabajan con los valores máximos, sino que lo hacen con los valores eficaces.

El *Valor eficaz* ( $V_{ef}$ ) y el *valor medio* ( $V_{med}$ ), de la corriente y voltaje senoidal, se calcula de la siguiente manera:

$$V_{ef} = \frac{1}{\sqrt{2}} V_{max} = 0.707 V_{max}$$

$$V_{med} = \frac{2}{\pi} V_{max} = 0.637 V_{max}$$

Cuando utilizamos un voltímetro para medir la **caída de tensión** (voltaje) en los extremos de un tomacorriente de la red eléctrica (corriente alterna), lo que en realidad medimos es el *Voltaje eficaz* ( $V_{ef}$ ).

Sabemos que el *voltaje eficaz* ( $V_{ef}$ ) de la red domiciliaria es ~ **220V** (~ es un símbolo de señal alterna), por tanto, el *Voltaje máximo* ( $V_{max}$ ) o *Voltaje pico* ( $V_{pp}$ ) es igual a:

$$V_{max} = \sqrt{2}V_{ef} = (\sqrt{2})(220 V) \approx 311 V$$

El Voltaje  $\emph{m\'aximo}$  ( $\emph{V}_{\emph{max}}$ ) de 311  $\emph{V}$  es posible medirlo y visualizarlo mediante un osciloscopio.

El símbolo de la fuente de voltaje de corriente alterna es

Los equipos electrónicos como la computadora, monitores, impresoras, escaneadores, entre otros, se instalan a la corriente alterna de ( $^{\sim}$  220 V), no obstante que todos ellos funcionan con corriente y voltaje continuo; esto se logra gracias a que los equipos disponen de una fuente de alimentación, cuya función es convertir la corriente alterna en corriente continua.

#### 1.2. Dispositivos semiconductores

Los dispositivos que procesan las señales alternas de baja potencia como la salida de un micrófono, y las señales de la red eléctrica, se realizan convenientemente con diodos y transistores construidos con material semiconductor.

Los semiconductores, son materiales de germanio o silicio, que presentan pocos electrones libres en su banda de valencia, por tanto, si hacemos circular corriente por éste material, observaríamos que no es un buen conductor, ni tampoco, un buen aislante.

Para que sean buenos conductores de portadores de carga, a cada oblea de silicio le agregan impurezas, proceso llamado "dopaje". Si lo dopan con arsénico o fósforo, se hace un buen portador de electrones (carga negativa) o material tipo N. Si lo impurifican con aluminio, indio o galio, el material será un buen portador de huecos (carga positiva) o material tipo P.

Silicio Dopado con arsénico o fósforo

Material

Tipo P

Silicio Dopado con aluminio, indio o galio

La utilización de semiconductores a gran escala, para el tratamiento de señales eléctricas, se realizó a partir de 1947, cuando el transistor fue inventado por los físicos J. Bardeen, W. Brattain y W. Shockley, de los laboratorios Bell en Estados Unidos.

En 1958, el ingeniero norteamericano Jack Kilby, logró la integración de seis transistores en una oblea de germanio. A partir de ese momento, la integración se realizó por cientos, miles y ahora millones de transistores en una sola oblea de silicio.

Los dispositivos que integran elementos electrónicos se llaman "circuitos

integrados" o chips, los hay desde aquellos que se utilizan para la realización de prácticas de electrónica digital, hasta potentes microprocesadores, capaces de procesar cientos de millones de instrucciones por segundo.

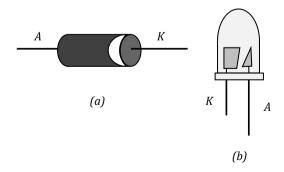

#### 1.2.1. **Diodos**

Un diodo es el más sencillo de los dispositivos semiconductores, pues, se trata de la unión de dos materiales de silicio, uno tipo P y otro tipo N.

Un diodo tiene dos terminales, uno de ellos adherido al material tipo P llamado **Ánodo (A)**, y otro conectado al material tipo N llamado **Cátodo (K)**.

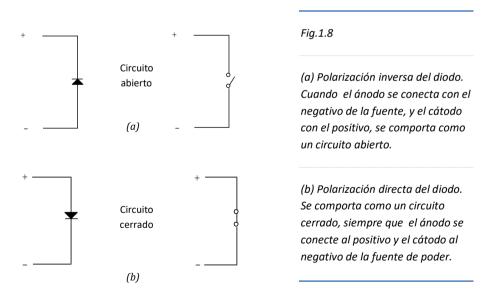

No obstante, su sencillez, el comportamiento eléctrico del diodo es muy valioso, pues puede funcionar como un interruptor, es decir, si se polariza convenientemente puede funcionar como un circuito cerrado o circuito abierto.

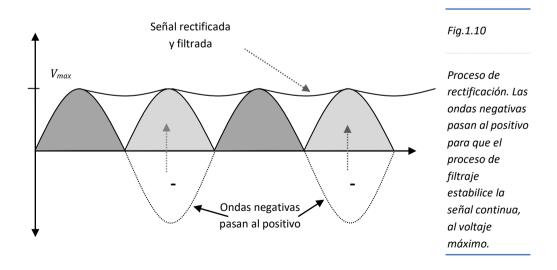

Además, el diodo es el principal responsable de la conversión de corriente alterna en corriente continua. Si se disponen adecuadamente los diodos, unos polarizados directamente y otros inversamente se obtiene un "rectificador" para dejar pasar ondas de una señal senoidal en un solo sentido. A ésta señal se le somete a un "filtraje" con ayuda del proceso de carga y descarga de un condensador.

Luego de éste procedimiento, se obtiene en los extremos del circuito de corriente continua un voltaje equivalente al valor máximo de la señal alterna, es decir, si rectificamos la corriente alterna de ~ 220 V (voltaje eficaz), en los terminales del circuito de corriente continua obtendremos un voltaje continuo de 311 V, este luego de un proceso de filtrado y atenuación.

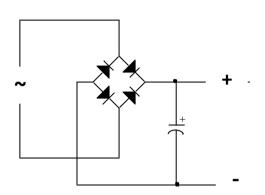

Fig.1.9

Rectificador tipo puente. La entrada recibe un voltaje de corriente alterna (~), mientras que la salida presenta un voltaje de corriente continua.

Lo mismo ocurre cuando rectificamos el voltaje en los extremos de un transformador reductor de ~220 V a ~9 V. Nótese que tanto la entrada como la salida del transformador poseen corriente alterna. La entrada al rectificador es ~9V y la salida será aproximadamente 12,7V de corriente continua.

Todas las fuentes de alimentación de los equipos de cómputo y demás artefactos electrónicos, cuentan con un sistema de rectificación para convertir el voltaje de corriente alterna en continua.

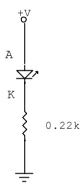

Existen varias clases de diodos especiales, entre los que se encuentran los diodos LED (diodos emisores de luz) y cuya importancia lo observamos en distintas aplicaciones de los circuitos electrónicos, en concreto, se utiliza para visualizar las salidas de las principales funciones lógicas en experimentación digital.

Los diodos LED, convierten la energía eléctrica en energía luminosa, ya sea en forma de luz visible o infrarroja.

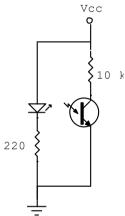

Para que los diodos LED emitan energía luminosa deberá polarizarse directamente y conectarse en serie con una resistencia de  $220\Omega$  o  $330\Omega$ . Con ésta configuración, la corriente que atraviesa es del orden de los miliamperios.

#### Fig.1.11

Polarización directa de un diodo LED (Light emiting diode), el ánodo conectado al positivo y el cátodo al negativo. El resistor de  $220\Omega$  puede instalarse en el terminal del ánodo o del cátodo y el efecto será el mismo.

La forma física de los diodos es muy diversa y está en relación con la aplicación y tratamiento de corriente.

Fig.1.12

Forma física de un diodo rectificador (a) y de un diodo LED (b). Obsérvese que el cátodo en (a) se visualiza mediante una franja de color claro, mientras que en (b) el pin o patita del cátodo es más pequeño.

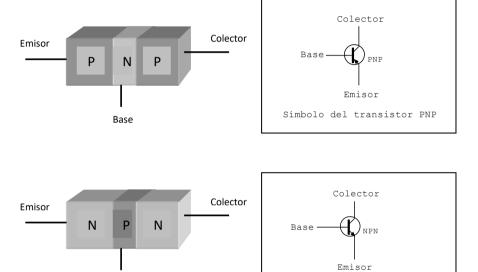

#### 1.2.2. Transistores BJT

Los transistores de unión bipolar (BJT), son dispositivos semiconductores que constan de tres materiales semiconductores tipo P y tipo N.

Si el transistor presenta dos materiales tipo P y uno tipo N, entonces será del tipo PNP, en cambio, si consta de dos materiales tipo N y uno tipo P, entonces constituirá un transistor tipo NPN.

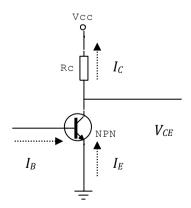

El transistor tiene tres contactos o pines llamados: *Emisor (e)*, *Base (b)* y *Colector (c)*.

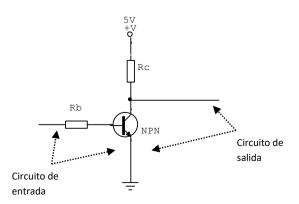

Cuando se configura el transistor de tal manera que el emisor sea común tanto para el circuito de entrada como para la salida, se llama configuración *Emisor común*.

Base

Fig.1.13

Símbolo del transistor NPN

Configuración Emisor común. La Base y el Emisor forman parte de la entrada de señal, mientras que el Colector y Emisor constituyen el circuito de salida de la señal. En el mundo de la electrónica, el transistor tiene múltiples aplicaciones, ya sea como amplificación de señales, interrupción, conmutación, regulación, etc; función que realiza tanto en el ámbito doméstico como industrial.

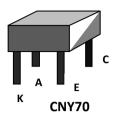

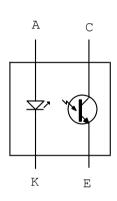

Muchos componentes de los equipos de cómputo utilizan un tipo especial de transistores que se activan mediante el "efecto fotoeléctrico", llamado fototransistor. Si a éste dispositivo se acopla una fuente de luz (LED), entonces constituirá un sensor de posición, ya que, si se interrumpe el haz de luz emitido, el fototransistor se activará indicando la presencia de algo.

Los sensores de posición son muy utilizados en los discos duros, impresoras, lectoras de DVD, y otros mecanismos donde sea necesaria la activación de motores o verificar la presencia de papel, entre otros.

El símbolo de un fototransistor es el siguiente

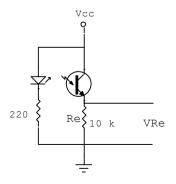

En electrónica digital, el transistor se utiliza básicamente como interruptor, puesto que, se necesita representar físicamente los dos estados de una variable lógica, el cero y el uno. El *cero* constituye un *circuito abierto*, mientras que el *uno* implica un *circuito cerrado*.

Según la tecnología de fabricación, los transistores se clasifican en dos: transistores bipolares (BJT) y transistores de efecto de campo (FET).

La tecnología MOSFET, una variante mejorada de los transistores FET, permiten una mejor integración en los circuitos integrados, por tal motivo, en la construcción de circuitos integrados digitales, básicamente utilizan ambas tecnologías: *TTL* (transistor transistor Lógico) y los *CMOS* (semiconductor metal oxido complementario).

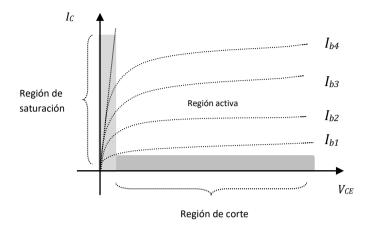

#### 1.2.2.1. Zonas de trabajo del transistor

El funcionamiento del transistor se efectúa en tres regiones: activa, corte y saturación. Estas zonas de trabajo se determinan teniendo en cuenta la corriente de *Colector (Ic)* y la caída de *tensión entre el Colector y Emisor (V\_{CE})*.

El transistor trabaja en la **región activa** ó modo de operación "lineal" cuando es necesario tratar una señal débil y permitir su respectiva amplificación en función a la ganancia del dispositivo.

Lo hace en la *región de corte* y *saturación* sólo cuando se requiere que el transistor funcione como una variable lógica ó como circuito de conmutación. Este modo de trabajo se conoce como "no lineal".

NPN

Fig.1.14

Zonas de trabajo del transistor. Nótese que en la región de corte la corriente de Colector es muy pequeña, mientras que en la región de saturación es muy alta. La corriente de Colector es correspondiente con la corriente de Base.

Un transistor trabaja en zona de corte cuando la corriente de base es aproximadamente cero. El voltaje entre Colector y Emisor es aproximadamente el voltaje de la fuente. Esta situación implica que la corriente de Colector sea aproximadamente cero, y la caída de tensión en el resistor de Colector también sea casi nula.

En cambio, para un transistor que trabaja en la zona de saturación, circulará por la Base una corriente de Base máxima, lo que conlleva a que la corriente de Colector sea también máxima. Cuando ocurre éste modo de trabajo, la caída de tensión en el resistor de Colector será aproximadamente el voltaje de la fuente de poder, y la caída de voltaje entre Colector y Emisor será aproximadamente cero.

Fig.1.15

Ley de Kirchoff para las corrientes se determina así: La corriente de Emisor es igual a la suma de la corriente de Base con la de Colector.

Asimismo, la ley de mallas de Kirchoff, se verifica del siguiente modo: El voltaje de fuente es igual a la suma del voltaje entre Colector y Emisor, más el producto de la corriente de Colector y la resistencia de Colector.

Para analizar estos dos estados o zonas de trabajo, sólo lo haremos en la malla Colector Emisor, asumiendo que en la malla Base Emisor se dan todas las condiciones necesarias para llevar al transistor a corte o saturación.

En la malla Colector Emisor, el voltaje de salida  $\equiv V_{CE}$ , tenemos:

$$V_{cc} = IcRc + V_{CE}$$

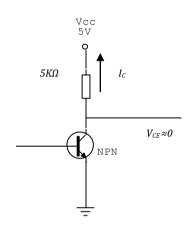

Ejemplo: Calcule la corriente de Colector ( $I_c$ ) que circula por Rc =5 $K\Omega$ , si el transistor trabaja en saturación y cuya la fuente de energía (Vcc) es +5V.

Cuando el transistor trabaja en la región de saturación  $V_{CE} = 0$

$$V_{cc} = I_C R_C$$

$$I_C = \frac{5V}{5\,000\Omega}$$

$$I_C = 1mA$$

La corriente máxima de Colector que circulará por la malla es 1*mA*.

En términos reales la región de saturación trabajará con corrientes de Colector ligeramente menores a 1mA, produciéndose a su vez un incremento en el voltaje Colector Emisor.

De igual manera, en la región de corte, la corriente de Colector no será necesariamente cero, sino ligeramente superior, lo que conlleva la presencia de una pequeña caída de tensión en la resistencia de Colector, lo que a su vez disminuye ligeramente el voltaje Colector Emisor.

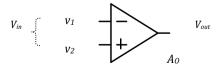

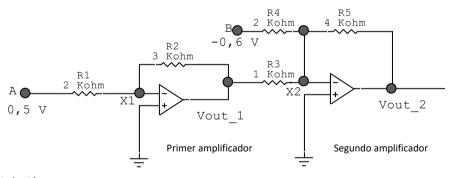

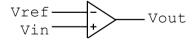

#### 1.2.3. Amplificadores operacionales

El amplificador operacional (amp op), es un circuito amplificador de alta **ganancia** ( $A_0$ ) cuya respuesta a una señal de entrada se controla mediante un enlace de retroalimentación.

Fig.1.16

Símbolo del amplificador operacional.

En general, el voltaje de salida ( $V_{out}$ ) depende del voltaje de entrada ( $V_{in}$ ) y de la función de transferencia o ganancia ( $A_0$ ).

$$V_{out} = A_O V_{in}$$

Las entradas  $v_1$  y  $v_2$  se llaman terminales de entrada diferencial, pues el voltaje de entrada  $v_i$ , es la diferencia de voltajes entre ellas.

$$V_{out} = A_O(v_2 - v_1)$$

La entrada rotulada con el signo (-) se denomina *terminal inversora*, mientras que la designada con el signo (+), *terminal no inversora*.

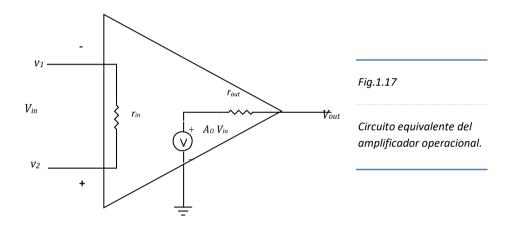

Los valores típicos de un amplificador operacional están en base a la estructura interna del mismo.

- La resistencia de entrada  $(r_{in})$  es muy alta, mayor que 100 k $\Omega$ ; por tanto, la corriente que circula por ella es muy pequeña, aproximadamente, cero. Idealmente, no fluye corriente.

- La ganancia  $(A_0)$ en lazo abierto (sin retroalimentación) es bastante alta, superior a 100 000. Idealmente se considera infinito.

- La resistencia de salida es muy baja, inferior a  $100\Omega$ . Idealmente se considera cero.

- Idealmente, el voltaje de salida  $(V_{out})$  es cero cuando el voltaje de entrada  $(V_{in})$  es cero. Característica denominada "Tensión de salida sin offset". Sin embargo, las características reales del amplificador originan un voltaje en la salida cuando el voltaje de entrada es cero. Esta diferencia de potencial de denomina "voltaje de desnivel". Algunos amplificadores disponen de terminales para anular dicho voltaje.

- Ancho de banda BW es cero. El amplificador en lazo abierto, la ganancia varía con la frecuencia de la señal, ocasionando que el dispositivo trabaje en un intervalo finito de frecuencias.

#### Configuraciones del amplificador operacional

Las configuraciones que se pueden realizar con el amplificador son tres:

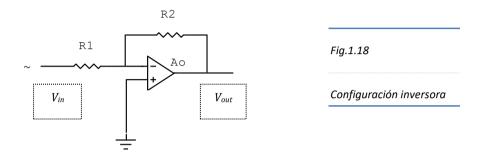

- Configuración inversora

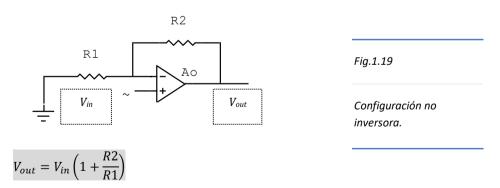

- Configuración no inversora

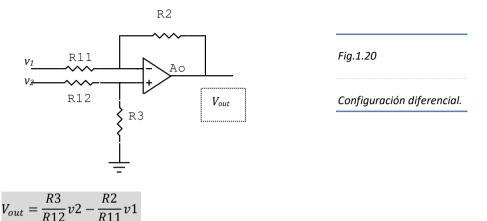

- Configuración diferencial

$$V_{out} = -V_{in} \frac{R2}{R1}$$

La ganancia en lazo cerrado  $(A_{LC})$ , está expresado por  $\frac{R^2}{R^2}$ ; y el signo negativo revela la propiedad de inversión del circuito.

La ganancia de esta configuración está expresado por  $\left(1+\frac{R^2}{R^2}\right)$ ; en donde se observa que si R2 es cero, la ganancia es la unidad.

Asimismo, se verifica la propiedad de no inversión de la señal de entrada.

El amplificador operacional cuenta con dos terminales de alimentación (fuente positiva y fuente negativa), aunque también se puede instalar una fuente positiva; dependiendo si en la salida queremos una señal con ondas positivas y negativas o sólo obtener ondas positivas.

Todos los circuitos amplificadores con operacionales se basan en las tres configuraciones anteriores.

En lo que se refiere a las aplicaciones de los amplificadores operacionales, el desarrollo vertiginoso de la computadora no marcó la desaparición de los amplificadores operacionales, al contrario, han logrado establecerse en diversos campos de importancia, desde la adecuación de señales de sensores de temperatura, luz, presión, etc. hasta controles de diversos componentes de envergadura industrial, bioingeniería o uso militar.

#### 1.3. Señales analógicas y digitales

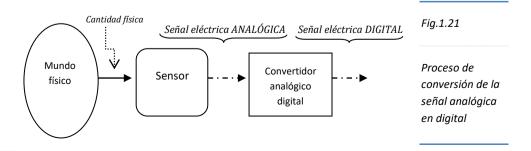

El mundo físico es analógico, pues, las principales magnitudes como la electricidad, presión, temperatura, luminosidad, entre otros, toman un valor dentro de un rango de posibilidades, mientras que, las magnitudes digitales no pueden adoptar cualquier valor, sino que, admiten sólo algunos valores enteros.

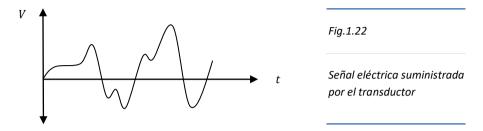

## 1.3.1. Señales analógicas

Es aquella señal eléctrica proporcionada por el sensor o "transductor", cuya característica es la variabilidad continua de sus valores.

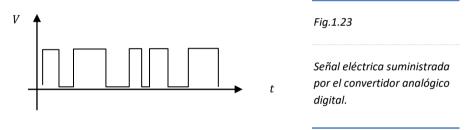

## 1.3.2. Señales digitales

Son señales eléctricas provenientes del convertidor analógico digital, luego de procesar la señal analógica. Se caracteriza porque adopta valores discretos de una posibilidad restringida.

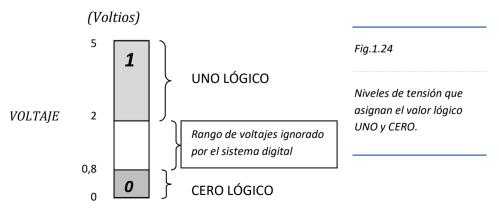

## 1.3.3. Lógica digital

En los sistemas de cómputo se asume un NIVEL BAJO como CERO y un NIVEL ALTO como UNO. En los aspectos prácticos, sin embargo, los circuitos electrónicos digitales consideran un rango de voltajes y los asumen como UNO o como CERO.

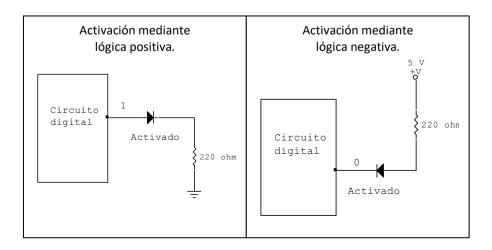

## 1.3.4. Lógica positiva y lógica negativa

En electrónica digital es usual trabajar con lógica de voltajes. Si se asume que el nivel de voltaje alto o más positivo corresponde al UNO lógico y el nivel de voltaje bajo o menos positivo, al CERO lógico, se denomina "lógica positiva".

Sin embargo, si el nivel de voltaje alto corresponde al CERO lógico y el nivel de voltaje bajo al UNO lógico, se designa, "lógica negativa".

## Problemas Resueltos Nº 01

Para resolver los problemas planteados a continuación se debe tener en cuenta los prefijos de los múltiplos y submúltiplos de las cantidades físicas.

|         | <u>Múltiplos</u>       |         |         | Sub múltiplos     |         |

|---------|------------------------|---------|---------|-------------------|---------|

| Prefijo | Valor                  | símbolo | Prefijo | Valor             | símbolo |

|         | numérico               |         |         | numérico          |         |

| Tera    | 10 <sup>12</sup>       | Т       | pico    | 10 <sup>-12</sup> | р       |

| Giga    | <b>10</b> <sup>9</sup> | G       | nano    | 10 <sup>-9</sup>  | n       |

| Mega    | 10 <sup>6</sup>        | M       | micro   | 10 <sup>-6</sup>  | μ       |

| Kilo    | 10 <sup>3</sup>        | K       | mili    | 10 <sup>-3</sup>  | m       |

Unidad 10<sup>0</sup> = 1

- 1. Realizar las conversiones de las siguientes cantidades:

- a. 85 milivoltios (mV) a voltios (V).

#### Solución:

Se expresa 85 mV en potencia de 10

$$85x10^{-3} V = 0.085 V$$

Que es lo mismo dividir 85 entre 1000, ó correr la coma decimal tres posiciones a la izquierda de 85.

b. 635 microamperios (μA) a amperios (A).

#### Solución:

635 µA expresado en potencia de 10.

$$635x10^{-6} A = 0.000635 A$$

Es decir, 635 entre 1 000 000, ó correr la coma decimal seis posiciones a la izquierda de 635.

c. 0,048 Watts (W) a miliwatts (mW).

#### Solución:

0.048 W se expresa en potencia de 10, ya que 10<sup>-3</sup> es el prefijo (mili).

$0,048~W=0,048x10^{-3}x10^3$  , nótese que también se multiplicó por  $10^3$  para que la expresión inicial no cambie.

$$(0.048x10^3)x10^{-3} W = 48x10^{-3} W = 48 mW$$

d. 150000 Ohmios ( $\Omega$ ) a megaohmios ( $M\Omega$ ).

## <u>Solución</u>:

150 000  $\Omega$  se expresa en potencia de 10, pues 10<sup>6</sup> es prefijo de (mega).

$$150\ 000\ \Omega = 150\ 000\ x\ 10^6 x 10^{-6}\ \Omega$$

$$\frac{150\ 000}{1\ 000\ 000}x10^{6}\Omega=0,15x10^{6}\Omega=0,15\ M\Omega$$

e. 80 000 milicoulombs (mC) a coulombs (C).

## <u>Solución</u>:

80 000 mC se expresa en potencia de 10.

$$80\ 000\ x\ 10^{-3}\ C = \frac{80\ 000}{1000}\ C = 80\ C$$

f. 6 amperios (A) a miliamperios (mA).

#### Solución:

$6\,A=6\,x\,10^{-3}\,x\,10^3\,A$ ; en este caso,  $6\,A$  se multiplicó por  $10^{-3}$  para obtener el prefijo mili, y también se multiplicó por  $10^3$  para mantener los  $6\,A$ .

$$6 x 10^3 x 10^{-3} A = 6 000 x 10^{-3} A = 6 000 mA$$

Determinar la energía potencial eléctrica de una batería utilizada en equipos de energía solar el cual tiene las siguientes especificaciones: 12 V, con 110 amp-hr. Solución:

Frecuentemente, la cantidad de carga de una batería se expresa mediante el producto amp-hr (amperios)(horas).

De la definición de corriente eléctrica I=dQ/dt, tenemos: Q=(I)(t), es decir, Q=110~amp-hr=110~A~x~3600s=396~000~C; pues 1hr es igual a 3 600 s. De la definición de voltaje tenemos:  $\Delta U=VxQ=(12~V)(396~000~C)=4~752~000~joulios=4,75~M$

3. Un monitor LCD de 20" durante su funcionamiento consume 144 000 joulios de energía durante una hora. ¿Cuál es la potencia de dicho monitor? Solución:

La potencia se calcula: P = W/t, donde W se expresa en joulios y t en segundos.

Reemplazando valores tenemos:

$$P = \frac{144\ 000\ J}{3\ 600\ s} = 40\ W$$

4. ¿Cuánta corriente circula por una motobomba de 0,5 HP de potencia, si se sabe que el voltaje de línea es ~ 220 V?

#### Solución:

Normalmente la potencia de los motores eléctricos se expresa en Horse Power (HP), cuya equivalencia en Watts (W) es la siguiente: 1 HP = 746 W.

Como la motobomba se conecta al voltaje alterno de 220 V, la corriente se calcula de la siguiente manera: I=P/V

$$I = \frac{(0,5)(746) W}{220 V} = 1,69 A$$

- 5. A la línea de voltaje (220 V) se conecta un motor de 440 W a un circuito de control de celeridad, cuya resistencia variable se encuentra en 176  $\Omega$ .

- a. ¿Qué corriente circula por el motor?

- b. ¿Cuál es la corriente máxima que puede circular por el motor?

- c. ¿Cuál es el valor mínimo de la resistencia variable para que la corriente sea máxima?

#### Solución:

38

La resistencia variable de éste circuito representa el control de celeridad de un motor. A menor resistencia, mayor celeridad (velocidad) del motor.

$$I = \frac{voltaje\ de\ l\'inea}{resistencia\ variable} = \frac{220\ V}{176\ \Omega} = 1,25\ A$$

b. Para saber cuánta corriente puede circular por el motor, se toma en cuenta la potencia del motor y el voltaje de línea.

$$I = \frac{potencia\ del\ motor}{voltaje\ de\ linea} = \frac{440\ W}{220\ V} = 2\ A$$

c. Para calcular el valor de la resistencia variable donde la corriente sea máxima, sólo tenemos que dividir el voltaje de línea entre la corriente máxima que

puede circular por el motor.

$$R = \frac{voltaje \; de \; linea}{corriente \; m\'axima} = \frac{220 \; V}{2A} = 110 \; \Omega$$

Observación: si la resistencia variable es menor de 110  $\Omega$ , entonces circulará mayor corriente, es decir, mayor de 2 A, circunstancia que dañará al motor.

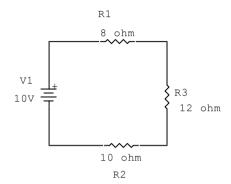

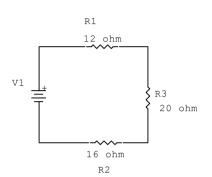

- 6. En el siguiente circuito, calcular:

- a. Resistencia total (equivalente serie)

- b. Corriente total

- c. Potencia disipada por R3

#### Solución:

a. Calculamos la resistencia total. Como el circuito es serie, se suman todas sus resistencias.

$$Rt = 8 \Omega + 10 \Omega + 12 \Omega = 30 \Omega$$

b. Calculando la corriente total.

$$I = \frac{10 V}{30 \Omega} = 0.333A = 333 mA$$

c. Calculando la potencia disipada por la resistencia R3. Se sabe que P = VxI, y que V = IxR; reemplazando en la ecuación anterior tenemos:

$$P = (IxR)xI = I^2R$$

$$P = (333 \text{ mA})^2(12 \Omega) = (333x10^{-3} \text{A})^2(12 \Omega) = 3996x10^{-3} W = 3,99 \text{ mW}$$

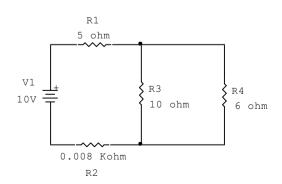

- 7. En el siguiente circuito paralelo, calcular:

- a. Resistencia equivalente.

- b. Corriente total.

#### Solución:

a. En primer lugar, se observa que R3 y R4 están en paralelo, por lo tanto, encontramos la resistencia equivalente en paralelo.

$$\frac{1}{Req} = \frac{1}{10\Omega} + \frac{1}{6\Omega} = \frac{4}{15\Omega}$$

$$Req = \frac{15}{4} = 3,75 \Omega$$

Las resistencias R1, R2 y Req están en serie, por tanto:

$$Rt = 5\Omega + 0.008x10^{3}\Omega + 3.75\Omega = 16.75\Omega$$

b. La corriente total que circula por el circuito es:

$$I = \frac{10 \, V}{16,75} = 0,597 \, A = 597 \, mA$$

8. Las resistencias del siguiente circuito disipan las correspondientes potencias:

R1: 3 W

R2: 4 W

R3: 5 W

- a. Hallar el voltaje de la fuente del circuito.

- b. Hallar la corriente total del circuito.

#### Solución:

a. Encontramos la caída de voltaje en cada una de las resistencias, ya que el voltaje total del circuito es la suma de los voltajes que caen en cada resistencia.

Si reemplazamos I = V/R en P = VxI, tenemos:

$$P = V\left(\frac{V}{R}\right) = \frac{V^2}{R}$$

Voltaje en R1:

$$V1 = \sqrt{P1.R1} = \sqrt{(3W)(12\Omega)} = 6V$$

Voltaje en R2:

$$V2 = \sqrt{P2.R2} = \sqrt{(4W)(16\Omega)} = 8 V$$

Voltaje en R3:

$$V3 = \sqrt{P3.R3} = \sqrt{(5W)(20\Omega)} = 10 V$$

El voltaje total (Vt) se calcula así:

$$Vt = V1 + V2 + V3 = 6V + 8V + 10V = 24V$$

b. Como el circuito es serie, la resistencia total es:

$$Rt = 12 \Omega + 16 \Omega + 20 \Omega = 48 \Omega$$

La corriente total es:

$$I = \frac{24 V}{48 \Omega} = 0.5 A = 500 mA$$

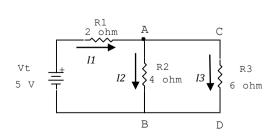

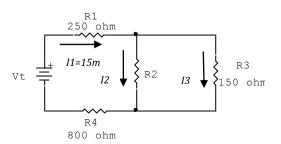

9. En el circuito de la figura calcular la corriente *I3*.

## Solución:

Se observa que los puntos A y C tienen la misma diferencia de potencial respecto a B y C que están

a un potencial eléctrico de 0 V. Por lo tanto, decimos que el voltaje que cae en R2 es igual al voltaje que cae en R3.

$$VR2 = VR3$$

$I2R2 = I3R3$

Entonces el voltaje total del circuito se distribuye de la siguiente manera:

$$Vt = VR1 + VR2$$

$$Vt = I1R1 + VR2$$

$$VR2 = Vt - I1R1 = I3R3$$

$$I3 = \frac{Vt - I1R1}{R3} \quad (*)$$

Para calcular *I3*, tenemos que determinar *I1*.

Se observa también que la corriente *I1* (corriente total) se reparte en el nodo A, en *I2* e *I3*.

$$I1 = I2 + I3,$$

Para calcular I1, se debe hallar primero la Resistencia total del circuito, donde R2 y R3 están en paralelo, y éstos están en serie con R1.

$$Rt = R1 + Req \frac{1}{Req} = \frac{1}{R2} + \frac{1}{R3} = \frac{R2 + R3}{R2R3}$$

$$Rt = R1 + \frac{R2R3}{R2 + R3}$$

$$Rt = \frac{R1R2 + R1R3 + R2R3}{R2 + R3}$$

$$Rt = \frac{((2)(4) + (2)(6) + (4)(6))\Omega^2}{(4+6)\Omega} = \frac{22}{5}\Omega = 4,4\Omega$$

Entonces la corriente total *I1*.

$$I1 = \frac{Vt}{Rt} = \frac{5 V}{4,4 \Omega} = 1,14 A$$

Reemplazando I1 en (\*) tenemos:

$$I3 = \frac{5 V - (1,14 A)(2 \Omega)}{6 \Omega} = 0,453 A = 453 mA$$

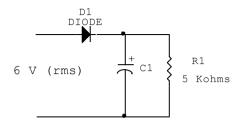

- 10. En el circuito rectificador de media onda cuya entrada es 6 V (rms), a 60 Hz y una resistencia de 5  $K\Omega$ , encontrar:

- a. El periodo de la señal eléctrica.

- b. El voltaje de caída (DC) en el resistor.

- c. La corriente máxima que circula por el diodo.

## Solución:

a. El periodo se calcula con el inverso de la frecuencia.

$$t = \frac{1}{f} = \frac{1}{60 \, Hz} = 0,0167 \, s = 16,7 \, ms$$

El voltaje que cae en el resistor de 5 KΩ

es voltaje de corriente continua, pues, el

diodo D1 rectifica media onda de la

ca la la fataisa de autore de El con decede

señal eléctrica de entrada. El condensador C1 contribuye en mantener la media onda rectificada a su Valor máximo.

Voltaje Máximo (Vmáx) =

$$(\sqrt{2})(Vef) = 6\sqrt{2} = 8,48 V$$

c. La corriente máxima que circula por el diodo es:

$$I = \frac{8,48 \, V}{5x10^3 \Omega} = 0,001696 \, A = 1,7 \, mA$$

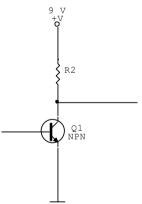

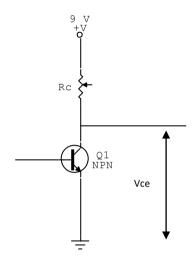

- 11. Un transistor trabajando en la zona de saturación presenta una corriente de colector de 750  $\mu$ A. Si el voltaje de fuente (Vcc) es 9 V.

- a. Calcular la Resistencia de colector (Rc).